[Перевод] Генерация и тестирование ядра RISC-V |

Как я писал в прошлом посте, название моего проекта на GSoC-2016 — «порт RISC-V на Parallella», и первая вещь, которую я должен был сделать, это познакомиться с экосистемой RISC-V. Один из лучших способов это сделать, — посмотреть видео с презентации первого воркшопа RISC-V на Youtube. Для того, чтобы понять самые важные концепции, я рекомендую следующие презентации:

Введение (Krste Asanovi'c) видео слайды

Тулчейн RISC-V (Andrew Waterman) видео слайды

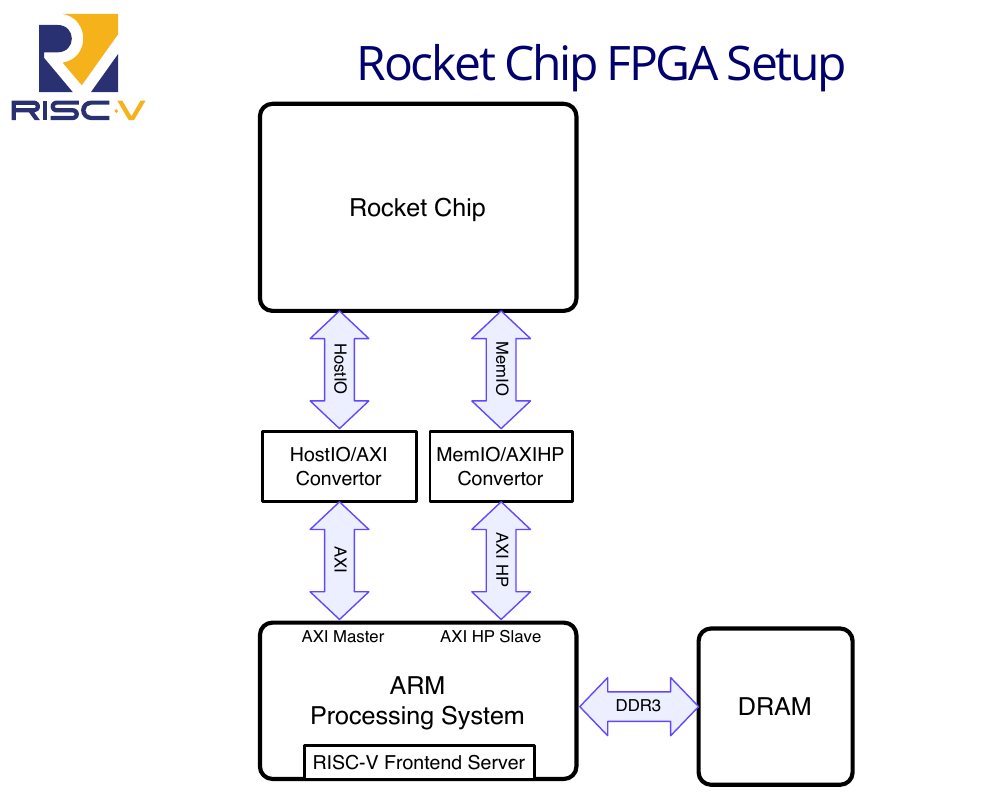

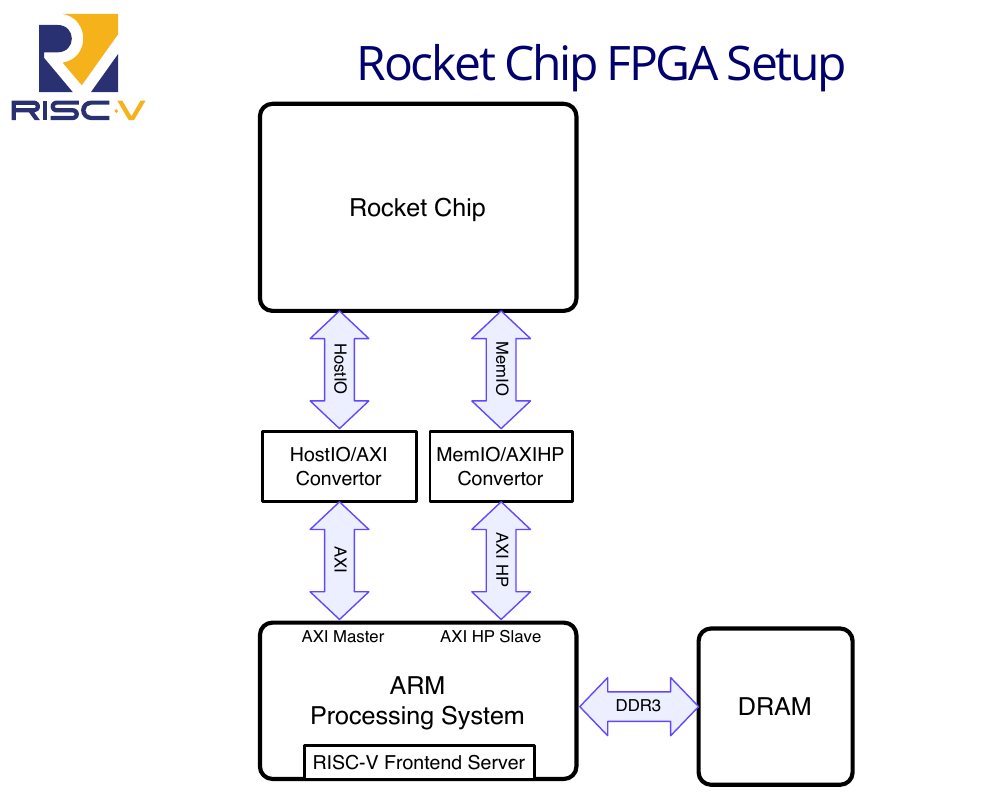

SoC-генератор RISC-V “Rocket Chip” в Chisel (Yunsup Lee) видео слайды

Структура программного стека RISC-V (Sagar Karandikar) видео слайды

Отладка на RISC-V (Albert Ou) видео слайды

Портирование нового кода на RISC-V с OpenEmbedded (Martin Maas) видео слайды

Окружение тестирования RISC-V (Stephen Twigg) видео слайды

Ещё одна ссылка, если вы интересуетесь Chisel, языком, основанным на Scala, который используется для описания текущей аппаратной реализации ядра RISC-V (ядро Rocket имеет in-order конвейер, BOOM — out-of-order), и любых будущих реализаций.

Краткое руководство по Chisel (Jonathan Bachrach) видео слайды

Работа с Rocket Chip, добавление расширений, инфраструктура ASIC и FPGA (Colin Schmidt) видео слайды

Если вы глубоко заинтересованы в RISC-V и развитии сообщества, я предлагаю вам принять участие в воркшопах.

Читать дальше ->

Метки:

author 32bit_me

тестирование it-систем

open source

fpga

risc-v

zynq

parallella

Введение (Krste Asanovi'c) видео слайды

Тулчейн RISC-V (Andrew Waterman) видео слайды

SoC-генератор RISC-V “Rocket Chip” в Chisel (Yunsup Lee) видео слайды

Структура программного стека RISC-V (Sagar Karandikar) видео слайды

Отладка на RISC-V (Albert Ou) видео слайды

Портирование нового кода на RISC-V с OpenEmbedded (Martin Maas) видео слайды

Окружение тестирования RISC-V (Stephen Twigg) видео слайды

Ещё одна ссылка, если вы интересуетесь Chisel, языком, основанным на Scala, который используется для описания текущей аппаратной реализации ядра RISC-V (ядро Rocket имеет in-order конвейер, BOOM — out-of-order), и любых будущих реализаций.

Краткое руководство по Chisel (Jonathan Bachrach) видео слайды

Работа с Rocket Chip, добавление расширений, инфраструктура ASIC и FPGA (Colin Schmidt) видео слайды

Если вы глубоко заинтересованы в RISC-V и развитии сообщества, я предлагаю вам принять участие в воркшопах.

Читать дальше ->

| Комментировать | « Пред. запись — К дневнику — След. запись » | Страницы: [1] [Новые] |