[�� ���������] ������������ MIPSfpga �� ������ ����� � ���������� ��������� � �������. ����� 1 |

MIPSfpga ������������ ����� ��������������� ��� ��������������� ����� �������������� MIPS32 microAptiv ����� Imagination, ������� ����� ���-������ � ���� ���������� �������. ��� ���������� �� ����� Verilog �������� ������������ � ����� �������������� ��� ������������� � ���������� ���������� �� FPGA �����.

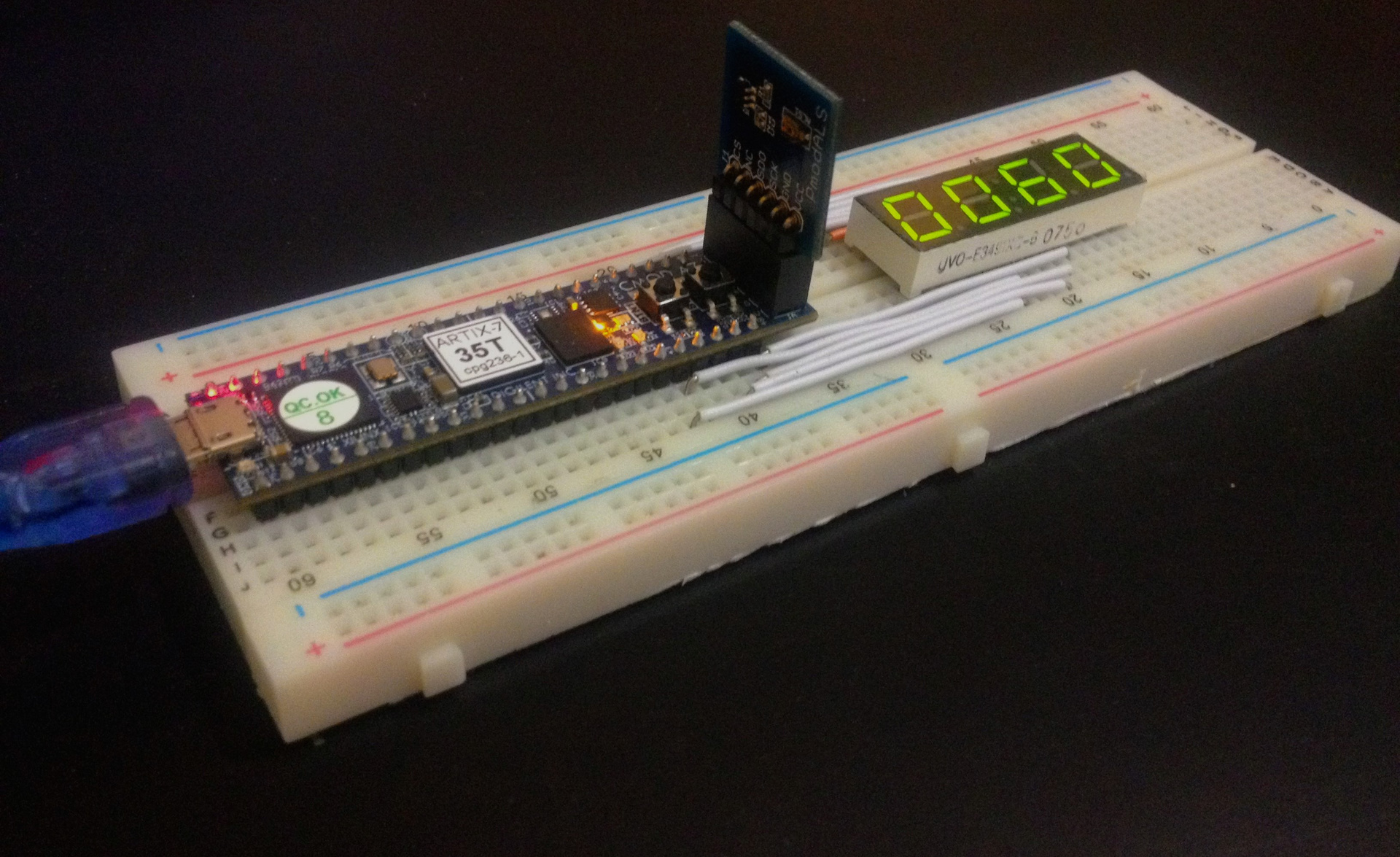

� ����� ������ ����� ������� �� ������� Digilent cmodA7 ��� ����������� ��������� MIPSfpga-plus �� ������ �����.

�� ����������� ���� MIPSFPGA ���������� �� ���������� ����� ����� ���� ��� ALTERA � Xilinx, ����� ��� Basys 3, Nexys4 ddr, � ������ (������ ������ ��������� �� github). ����� ����� �������� ��������� ����� ������������� �� FPGA. ���� �� ����� ����� �������� �� ���������, �� � ����������� ��������� � ���� MIPSfpga � �������������� ���������� EJTAG � �������� Bus Blaster ����� ����� 50$. ������� Bus Blaster �������� ������� �� ����������������� ������ USB 2.0 � ����������� �� � ���������������� �������� EJTAG, ��� ��������� ��������� ��������� � ���� MIPSfpga � ��������� �������� ��������, ������� �� ��� �����������. �������� � ������������ ������� Bus Blaster ���� ������ ��������� � ������� MIPSfpga ���� ���������. ��������� ������� ������� MIPSfpga, �������� MIPSfpga-plus �������� � ���� ����� ����� �������:

� ����������� �������� ������������ ����������� � �������������� USB-to-UART ���������� ����� � $ 5 FTDI ������ $ 50 Bus Blaster, ������� ������ �� ��� �� � ����� �������.

� ����������� �������� �������� ������� �� ���� � 50 ��� 25 ��� �� 1 �� (���� ���� � �������) ��� ���������� �� ������� ���������� � ������ ��������� �������, ������� ������� � ���-������ � ��������������� ��������.

� ������ ���������� ������� ������������ � ���������� SPI.

� ��������� ������������������ ������������� ������������ �����������, ������� ����������� � 1 �� ������ 32 �� ������, ��� ��������� ���������� MIPSfpga �� ����� ������� ����� ���� FPGA ��� ������������� ������� ������. ���������� UART ������� � ������: MIPSfpga � UART.

��� ������� � MIPSFPGA-plus �� ������ ����� Xilinx, ����� ���������� ������ ����. � ����� � ��������� �������� ����������� ��������� FPGA ���� � ���������� ������������ �������� �� �������������� ���������� ������������ ����������� ��� ������������� (� ������ �� ������� ������������ ������������ ������������� ���� MIPS microAptiv UP). ��������� ���: ��������� ������������ ����������� ������ ���������� ��� �������������?, ���������� �� ������������ ������� MIPSfpga+ � ����� ����� �� ������ ������ �� ����� ������:

1. ��� ������ ����� �������� ����� c �������� MIPSFPGA. ��������� ���������� � ��� ��� ��� �������:

-> mipsfpga-download-instruction

���� � ��� ��� ���� MIPSfpga ������� � ��������� ������������� usb-to-uart ��������������� (� ����� cmodA7, � ��� �� �� ������ ������ ������ ����� Xilinx ���� ���������� uart), �� ��� ����������� ������� ���������� ������ ���������� MIPSfpga-plus:

-> Mipsfpga-plus

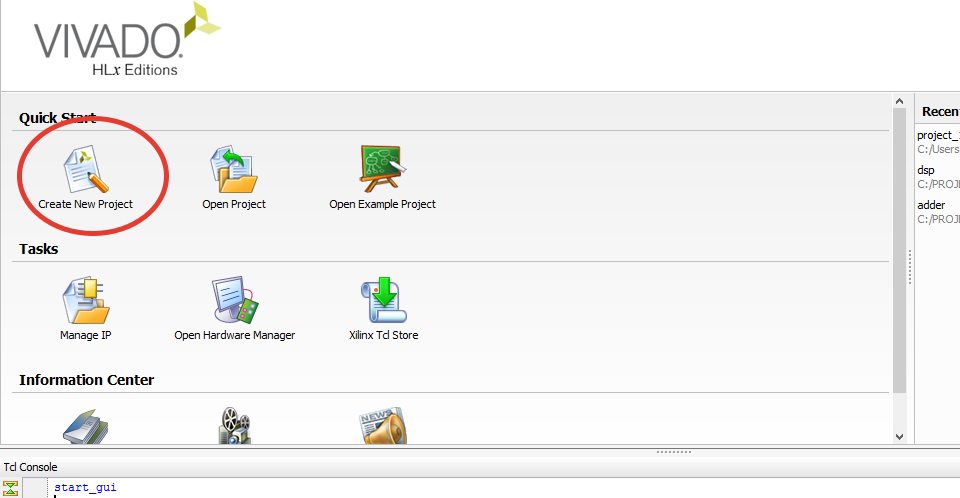

2. ��� ���� ����� Xilinx ������������ ����������� ����������� Vivado, ���������� ������ ����� ������� �� ������:

-> Download Vivado

3. ������ ������� �������� ����� ������ � Vivado:

�������� ��� ����� �������� ��������� ������:

���� �����:

�������� RTL ������ � ���� �����:

������ ������� ����� ������� ������������� MIPSfpga:

� ��� �� MIPSfpga-plus ������� ��������� � ������ �������� � mipsfpga-plus:

������� � ������ ������ uart � ������� ����� ��� ����:

���������� �������� IP � ������ ����������� �������� �� �����:

����� ����� ���� ������� ���������� ���� �������� ���� �����.

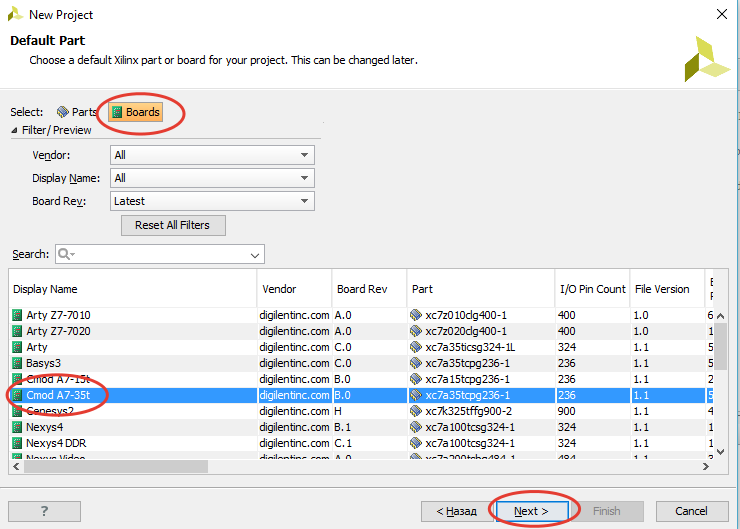

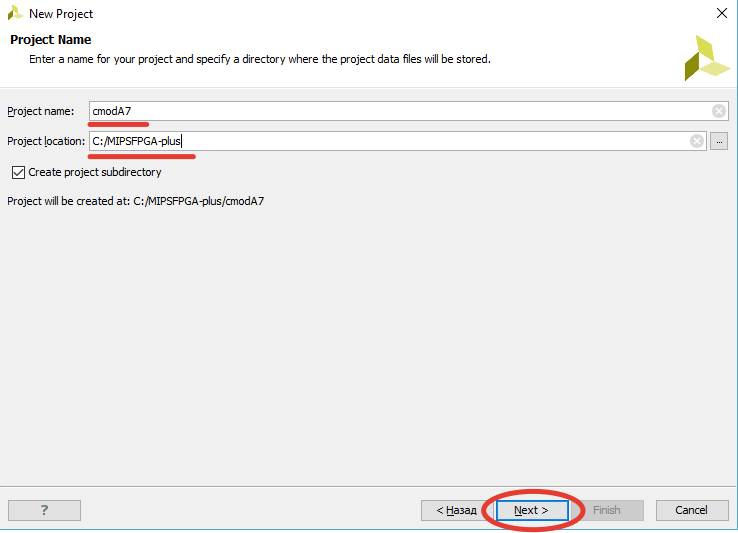

����� Digilent cmod A7 ���� ������� � ����� � �� �� ������� ����� � �������� ��� ������� �� ����� ����������. ����� ������� FPGA ����� ����� ��������� �� ���� ����� ������������, �� cmodA7 �������� ��� xc7a35tcpg236-1:

������ �������� �������� ���������� ����� ����� ����� � ���������� Vivado, ���� ������ ����� ��� ���, �� ������, ��������� �������� ����� ������� ��� ����, �� ������ ���� �� � ������� �������� ������������ block designer � Vivado, �� � ��� ����� �������������� �������������� ��� ������� ������ � ������������ �����, IP ������, � �.�. ������� �� ����� �� GitHub, ��������� ��� ����� ����� � ~\Vivado\2015.1\data\boards\ (��������� ��� Vivado 2015.1 � �����).

��� �� � ������� ������ � MIPSfpga-plus.

���� ������� �� �� ����� ����� cmodA7 ��������� ��� ��������� Artix-7, ����� 20800 LUT, 41600 FF, 225 KB ������� ������, ������� 48 �����, ����� ������� 2 �������� �������� ���, ����� ������� usb-uart ���������������, Quad-SPI Flash, � JTAG, 2 �������� ������, � ����� 5 ����������� 3 �� ������� ��� RGB (�������).

����� ��������� ������� MIPSfpga �� ����� cmodA7, �������:

��� 1. �������� ������-��������, ������� ������������� ������������ ����� �������/�������� MIPSfpga � �������/�������� ����� Basys3

��� 2. ��������� ����� ������ ������� MIPSfpga ��� ������������ ����� Basys3

��� 3. �������� ���� �����������, ������� ������������� ������������ ����� �������/�������� ����� � �������� ������� FPGA.

��������� cmoda7.v ��� ������� � �������� �������.

��� ��� �� ����� cmoda7 ��� �������������� ������� ����� ���� �� ������������ ��� ��������� ������� ���������� (��� ����������� ��������� � MIPSfpga-plus), ���� ������ ������ �� ��� ������� � ������ ��������. ��� �� ����� ��������� ����� EJTAG � �������� ������������ BUS Blaster.

��� ������ ����� �������� ������������ ���� ������������ ���� AHB_lite.

������������������� ���������������������� ���� (Advanced High-performance Bus, AHB) �������� �������� �����������, ������� ������������ �� ������ ����������������� ��������, �������� �� ����������. ���� AHB ��������� ����������� ���������� ���������� ���������. AHB-Lite �������� ���������� ������� AHB � ����� ������� �����������.

��� ������������ ����� ���� ������� ����������, ��������� MIPSfpga, � ��� �������: RAM0, RAM1 � GPIO, ������� ������������ ����� (��������������) ��� ����� ��� � ������ ������� � ����������� �����/������ �����. �� ��� ��� � ����� �������� � ������ GPIO � ������ ������ �������������� � ����������.

�������� �������� ����� �����-������:

i_clk � ������ ��������� ���������� ����� �������� (��� cmodA7 12 ���).

i_btn0 � ������ ������������ ��� ������������ ����������.

i_btn1 � n/c.

RsRx � ������ ������ �� uart.

seg, dp, an, � �������� ��� ����������� ��������������� 4 ���������� ����������.

led_r, led_g, led_b, � ������ ������������ �� ����� RGB Led.

JA � Pmod ���������.

��������� ��������� �������� ������ �������� ������� � reset (i_btn0) ��������� ��� ����������� ���������.

�������� ����� ������ cmoda7.v �������� �������� ���������� ������� MIPSfpga-plus (mipsfpga_sys) � �� ���������� � �������/�������� �����.

MFP_DEMO_LIGHT_SENSOR ����� ������������ ��� ������������ ������������ �������. ��� ����� �� ������ ������� mfp_system ����� 32-� ��������� ���� IO_7_SegmentHEX ������� �� ������� � ������ ����������� 4-� ���������� 7 ����������� ����������, ��������� � �������� ������ ���������� �mfp_multi_digit_display�:

��� �������� ����������� ����� ������ �������� �� ��������� � ����� ������ ��� �������.

��� ����������� ��������������� ���������� � ����� ������ ����� ����� ���:

��� ����� ������� �� ������� ��������� ������ clock � seven_segments ��������� ��������������� ������ bcd_to_seg, � ������������ ����� ��������� ���������� ������������ � ������� ������������ ��������� ������� �� ��������������� ������ (���� �������).

��� ��� �� ���� ���������� ��������� ������ � �������� � 50 ��� ������� �� �������� �����, ���� �� ����� � ����� �������� ������ �������� �� ���������� ��� ���� �� ����� �������� ��� ���������(��� ����������� ����������� �������� �� 7 ���������� ���������� ���������� ������� �������������� � 763 ��). ��� ����� ��������� ��������� �������� �������:

� �������� ������ �������� ������� � 50 M�� � 763 �� ���. ������� �� ������� ��� � ���� mfp_clock_dividers.v:

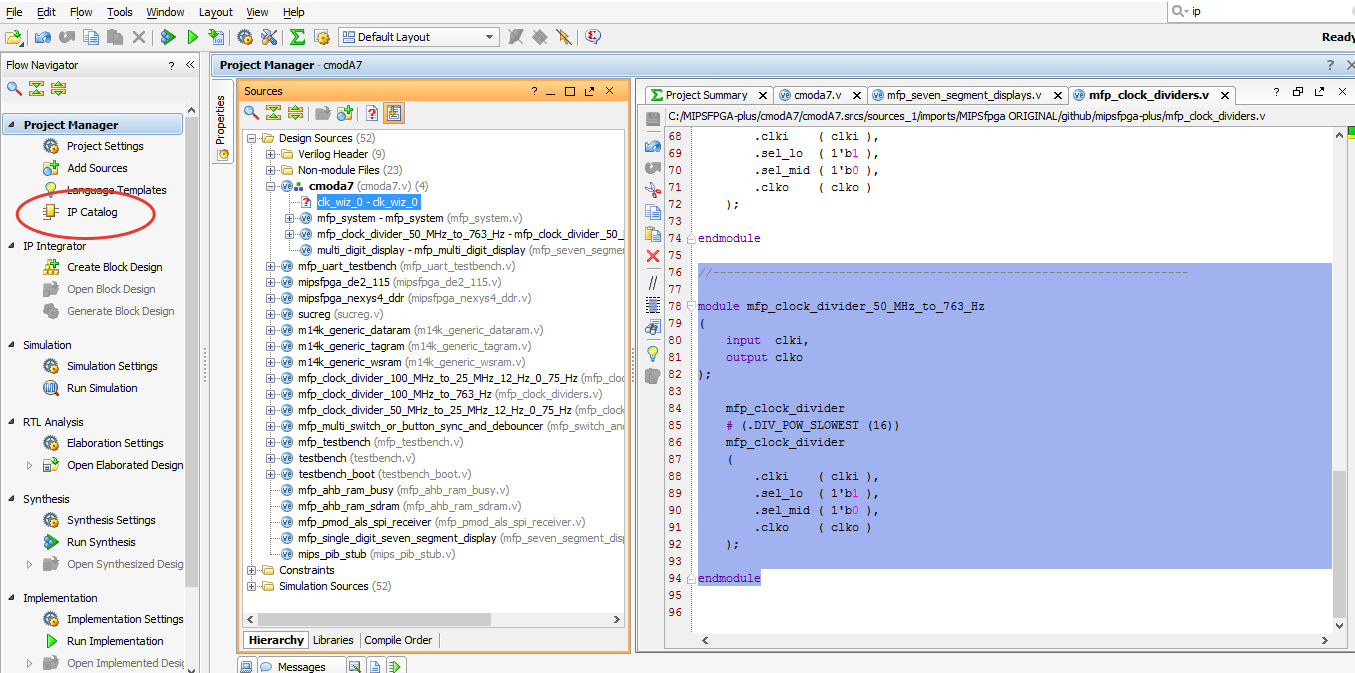

�� ���� ������� ��������� ������� reset � clock, RsRx, IO_Buttons. �� � ��� �� ����� ��� ������ ������ i_clk, � �� clock. ���� � ��� ��� �� ����� ������������ �������� ��������� � 12 ���, � ��������� � FPGA ����� �������� �� �������� 50 ��� � ����, � ��� ������ ���� � ��� ������ ����� � ������ �������� �������� (�������� Nexys 4 DDR ����� �������� ������� 100 ���). �������� �������� ��������� IP ���� Clocking Wizard (PLL), ��� ����� ������� IP �������:

������� Clocking Wizard:

������� board ��������� ��� ����, ���� ����������� ������ ��� ����� � ��������� �� ������� clocking options ����� ������� ���� MMCM ����� ����� ������� �������� ������� ������ 10...800���, ��� PLL 19...800���, ��������� �� cmoda7 ����� 12 ��� �������� MMCM, �� ��� ������ ���� ����� �������� ������ ���������:

�� ������� output clocks ������������� ������� 50 ��� (� �������� ����� � ����� ������������������, ��� �� ������ FPGA ����� ���� ������ ��������������):

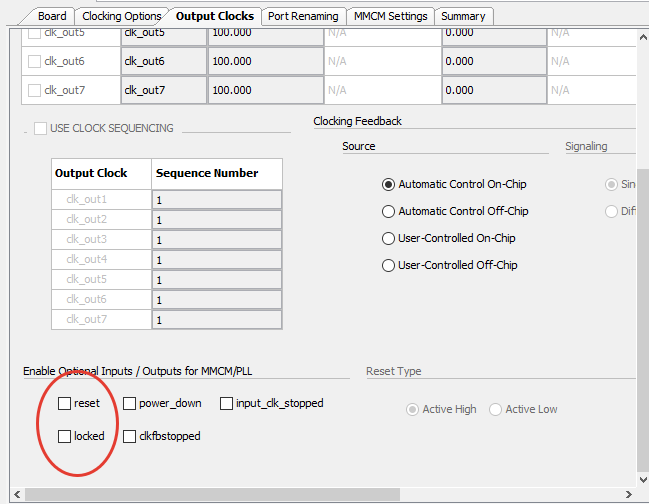

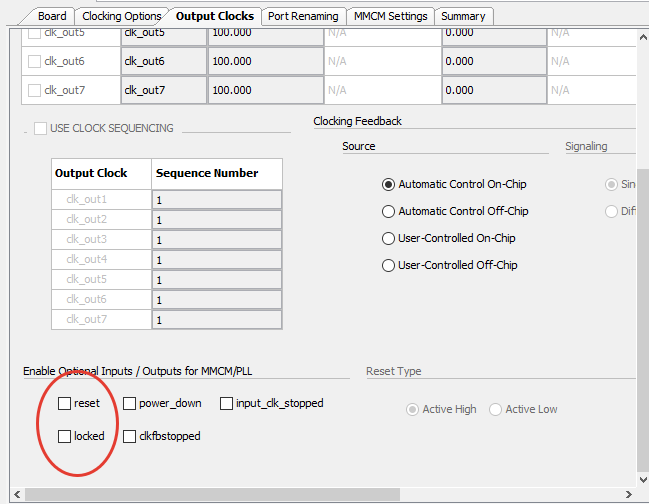

����� ������� reset � locked:

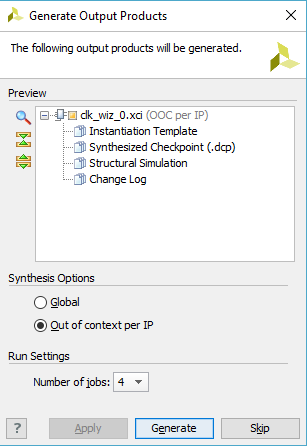

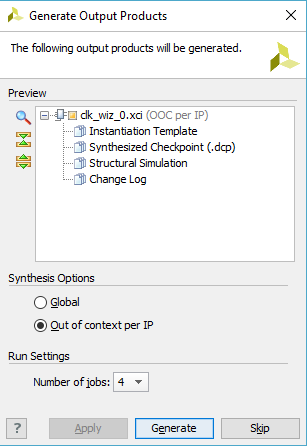

Port renaming, MMCM setting � Summary ������� � ��������� ��� ����, ���� ��, ��, � ��������� ���� �������� generate:

��������� ������� ������� ����������� ������������ ��� RGB Led, ��������� ��� ����� �� ����� � ��������� ��������� ��� ����� ������ ��������, � �� ����� ��� �� ��� ���� ���������:

� ����� �������:

������ �������� ������, �������� � ��������� ������� ������.

����� cmoda7 ����� 225 ����� �������� ������. ����� �������, ��� ����� ������ (128 ����� ��� ������ � 256 ����� ��� ��������) �� ���������� �� ����� cmoda7. ��� ���, ����������� ��� ����� ���������� � 32 �����, � ����� ���������� ����������� �������� ������� 64 �����. ����� �������, ����� ����������� ������ (32 K���� + 64 K���� = 96 K����) ������������� ������ ������ ����� cmoda7. ���������� 225-96 = 129 K���� ������ ����� ���� ������������ ��� ������ ���� ������� MIPSfpga, ��������, � �������� ���-������.

��������� ����� ������ �����, ������� ������ ������, ���������� � ������������ ����� Verilog ������� �� ���������� � ���� �������� �mfp_ahb_lite_matrix_config.vh�. ��������� ���� mipsfpga_ahb_const.vh. ������ ��� ������ (��� ��� ��������) ������� �� 13 ���. ����� �������, ����� ��� ������ ����� 213 32-������ ���� = 215 ���� = 32 K����.

������ ��� �������� ������� �� 14 ���. ����� �������, ����� ��� �������� ����� 214 32-������ ���� = 216 ���� = 64 K����.

������ �������� �cmoda7.xdc� ������� ������������� ������������ ����� �������� ��������� ������-�������� � �������� ������� FPGA ����� cmoda7 (xdc ���� � ������ ������� ������� ��� cmoda7):

��������, ��������� ������ ������������� ������������ ����� ������ i_clk � ������� ������� FPGA L17, �� ������� ��������� �������� ������ � �������� 12 ��� � ����� cmoda7.

��� �� � ���� ����������� ����� �������� ��������� �������� ��������� ����������� ��� ��������:

�� ����� �������������� ������������ �� ���� ����� ���������, ��� ����� ����� ����� � ���� ������������ �mfp_ahb_lite_matrix_config.vh� � ��������������� ������:

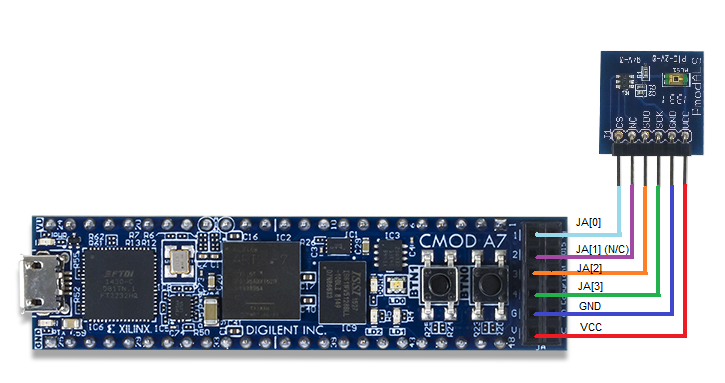

����� ������� �� ���������� ���������� �� Verilog ������ ���������� SPI � ���� AHB Lite ��� ���������� � �������� ������������ PmodALS ����� Digilent.

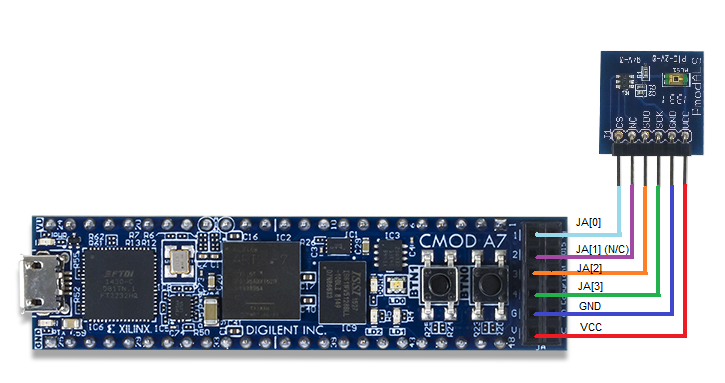

����� ����������� ���������� �� �������:

������ ��������� � ����� Pmod, ������ �������� ������� � �cmoda7.xdc� ��������� ��� JA[7..0].

��������� RTL ����� ����� ��������� �� ������� RTL Analisys -> Schematic, ��� ������ ���������� SPI �mfp_pmod_als_spi_receiver� ��������� � �mfp_system�:

��� �� ��������� � FPGA ��������� ������ ����� ������������� bitstream ���� �cmoda7.bit�, ��� ����� �� ������� Program and Debug -> Generate Bitstream � ��������� ���������� ��������:

����� �������� bitstream ����� ����� ��� ��������� � �����, ��� ����� �� ������� Program and Debug -> ������� Open Hardware Manager -> Open Target -> Auto Connect -> Program Device � �������� �������:

����� ��������� ����������� � �������� ������� ����� �������� ��������� � ��������� � ���� RAM1 ������� ��� �� ��������� � ���� AHB Lite.

��������� MIPSfpga ������������� � �������������� ������������ ���������� Codescape �������� Imagination. ���������� Codescape SDK � OpenOCD. Codescape ������������ ���������������� ��� �� ����� C, ��� � �� ����� ����������.

��� �������� ���� � ������� ����� ������� � ����� ��������� mipsfpga plus -> github -> mipsfpga-plus -> programs-> 01_light_sensor ������� �mfp_memory_mapped_registers.h�.

����� ������� main.c � ������� ���� �����:

����� � ����� ������� ������ ������� ����������� ���:

���������� motorola_s_record ����:

��������� � ������ ��� ����� ��������� USB UART ���������������:

�������� ���� 12_upload_to_the_board_using_uart:

��� � � ����� ��� �����, � �������� ��������� USB UART ���������������. � ��������� ���������:

��������� ������������ ������� ����� ���������� �� �����:

��� ��������� ������ ����������, � ����������� ��������� ����� ������� �� ����� �������� ���������� (Verilog, VHDL), � ��� �� ������������, ����������� ����������, ���������������� (����������� ������������� ���������) � ���������������� �� ����������, � ����� ���� ������� ��� ������� ��� ����� ����� � �������� ����� ��� ������� � ������������ ������������� ��������� ����� ��� ������� �������� � ������: ���������� ������� �����������, ����������� ���������� � ��������������� ���������������� �� ������� �����.

� ��������� ����� ����� ������� ��� ���������� ��������� ��������� � ������� MIPSfpga �� ������� ���������� Digilent Pmod KYPD, ���������� ���, � LCD ������� �� Nokia.

� ����� ������ ����� ������� �� ������� Digilent cmodA7 ��� ����������� ��������� MIPSfpga-plus �� ������ �����.

�� ����������� ���� MIPSFPGA ���������� �� ���������� ����� ����� ���� ��� ALTERA � Xilinx, ����� ��� Basys 3, Nexys4 ddr, � ������ (������ ������ ��������� �� github). ����� ����� �������� ��������� ����� ������������� �� FPGA. ���� �� ����� ����� �������� �� ���������, �� � ����������� ��������� � ���� MIPSfpga � �������������� ���������� EJTAG � �������� Bus Blaster ����� ����� 50$. ������� Bus Blaster �������� ������� �� ����������������� ������ USB 2.0 � ����������� �� � ���������������� �������� EJTAG, ��� ��������� ��������� ��������� � ���� MIPSfpga � ��������� �������� ��������, ������� �� ��� �����������. �������� � ������������ ������� Bus Blaster ���� ������ ��������� � ������� MIPSfpga ���� ���������. ��������� ������� ������� MIPSfpga, �������� MIPSfpga-plus �������� � ���� ����� ����� �������:

� ����������� �������� ������������ ����������� � �������������� USB-to-UART ���������� ����� � $ 5 FTDI ������ $ 50 Bus Blaster, ������� ������ �� ��� �� � ����� �������.

� ����������� �������� �������� ������� �� ���� � 50 ��� 25 ��� �� 1 �� (���� ���� � �������) ��� ���������� �� ������� ���������� � ������ ��������� �������, ������� ������� � ���-������ � ��������������� ��������.

� ������ ���������� ������� ������������ � ���������� SPI.

� ��������� ������������������ ������������� ������������ �����������, ������� ����������� � 1 �� ������ 32 �� ������, ��� ��������� ���������� MIPSfpga �� ����� ������� ����� ���� FPGA ��� ������������� ������� ������. ���������� UART ������� � ������: MIPSfpga � UART.

�������� ������� � Xilinx Vivado � MIPSfpga-plus

��� ������� � MIPSFPGA-plus �� ������ ����� Xilinx, ����� ���������� ������ ����. � ����� � ��������� �������� ����������� ��������� FPGA ���� � ���������� ������������ �������� �� �������������� ���������� ������������ ����������� ��� ������������� (� ������ �� ������� ������������ ������������ ������������� ���� MIPS microAptiv UP). ��������� ���: ��������� ������������ ����������� ������ ���������� ��� �������������?, ���������� �� ������������ ������� MIPSfpga+ � ����� ����� �� ������ ������ �� ����� ������:

1. ��� ������ ����� �������� ����� c �������� MIPSFPGA. ��������� ���������� � ��� ��� ��� �������:

-> mipsfpga-download-instruction

���� � ��� ��� ���� MIPSfpga ������� � ��������� ������������� usb-to-uart ��������������� (� ����� cmodA7, � ��� �� �� ������ ������ ������ ����� Xilinx ���� ���������� uart), �� ��� ����������� ������� ���������� ������ ���������� MIPSfpga-plus:

-> Mipsfpga-plus

2. ��� ���� ����� Xilinx ������������ ����������� ����������� Vivado, ���������� ������ ����� ������� �� ������:

-> Download Vivado

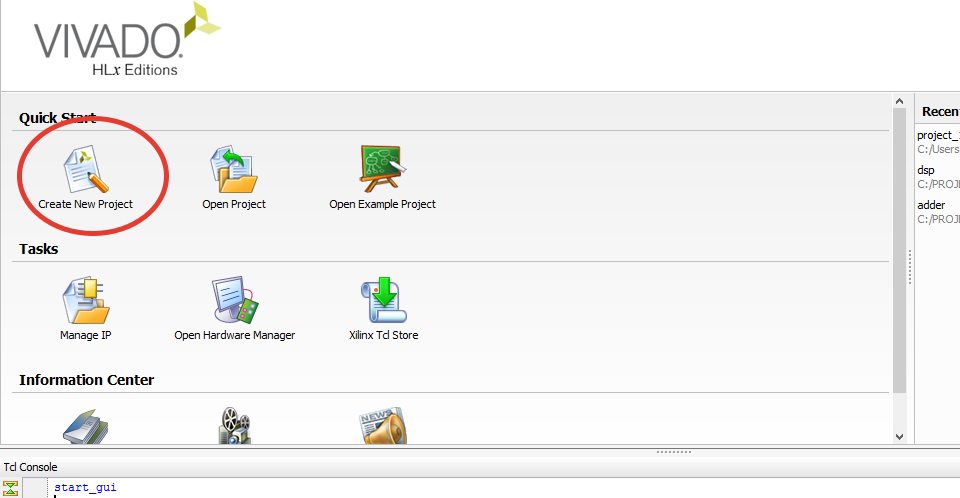

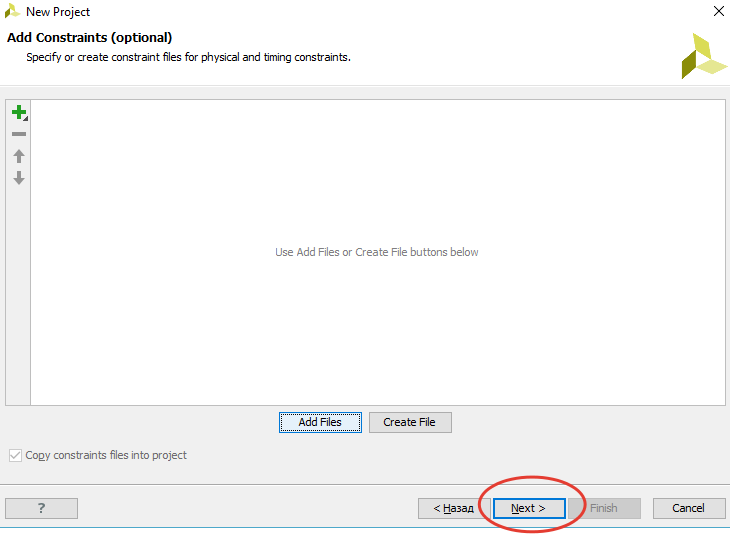

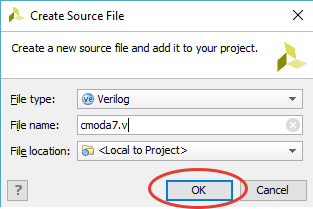

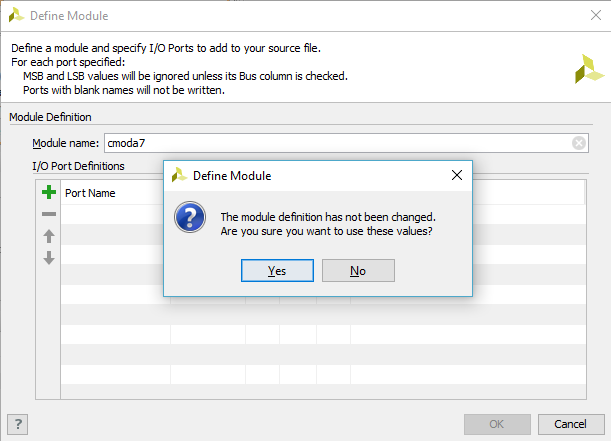

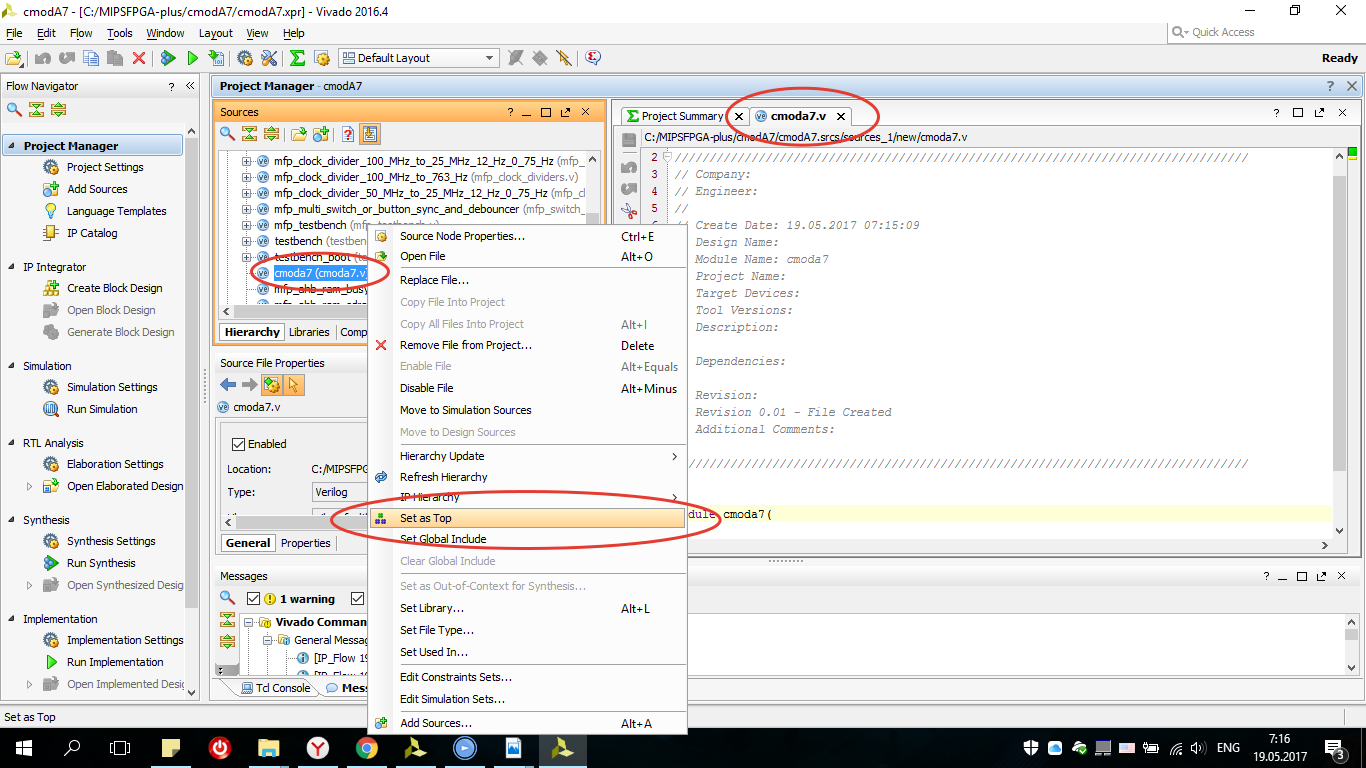

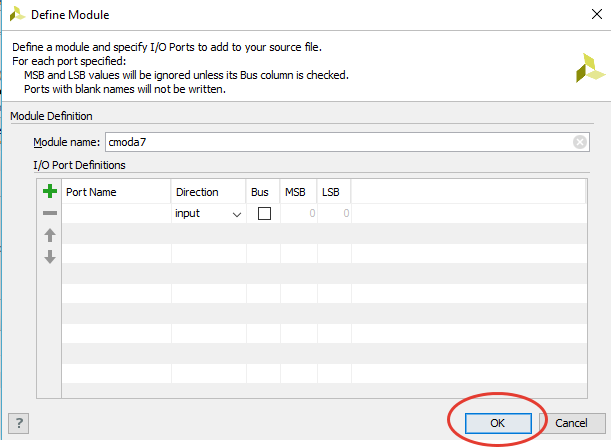

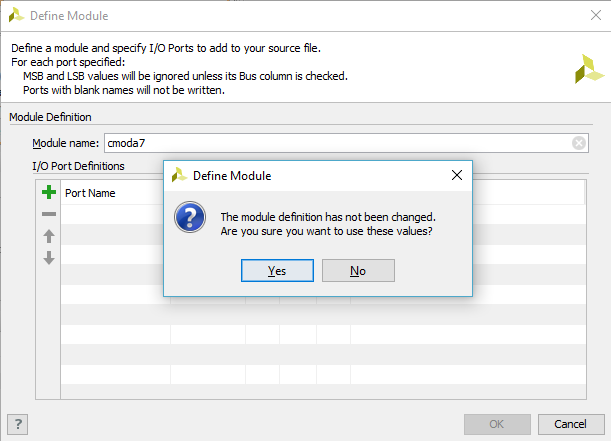

3. ������ ������� �������� ����� ������ � Vivado:

�������� ��� ����� �������� ��������� ������:

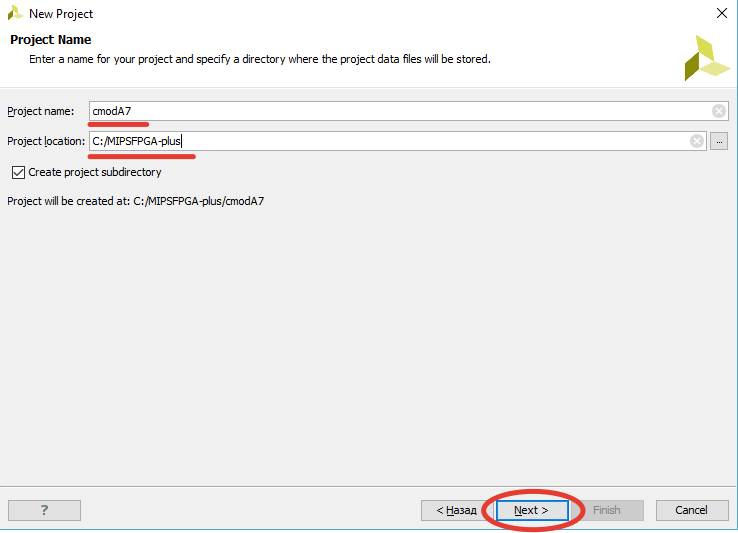

���� �����:

�������� RTL ������ � ���� �����:

������ ������� ����� ������� ������������� MIPSfpga:

� ��� �� MIPSfpga-plus ������� ��������� � ������ �������� � mipsfpga-plus:

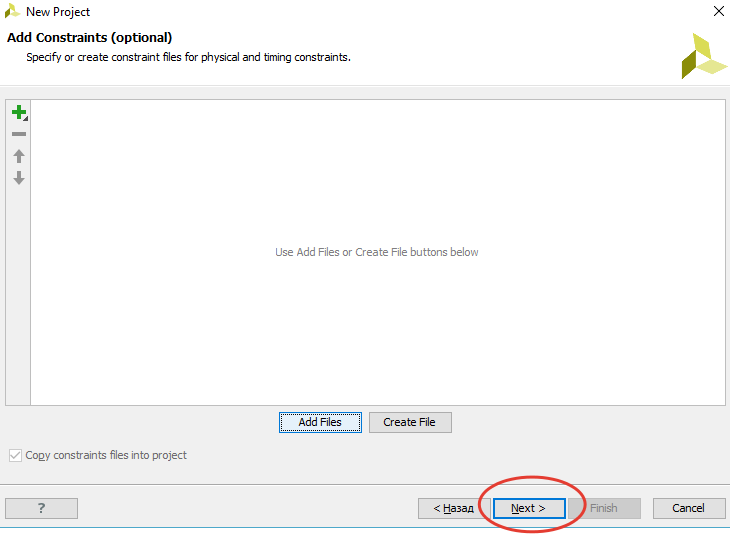

������� � ������ ������ uart � ������� ����� ��� ����:

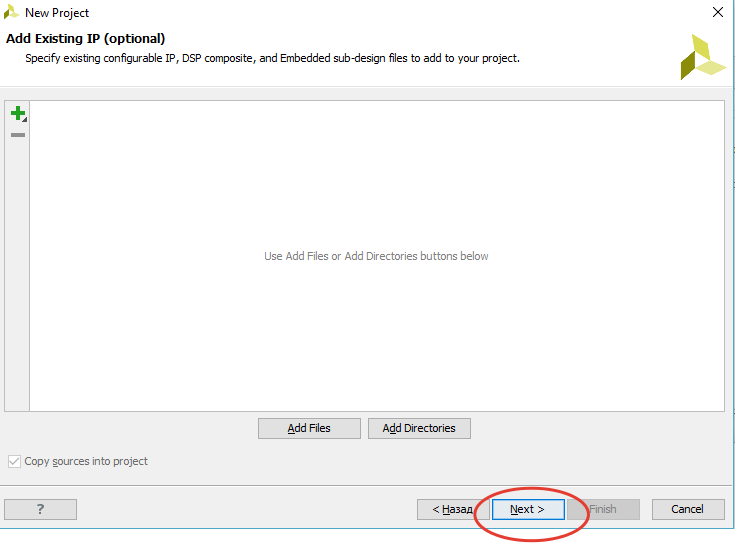

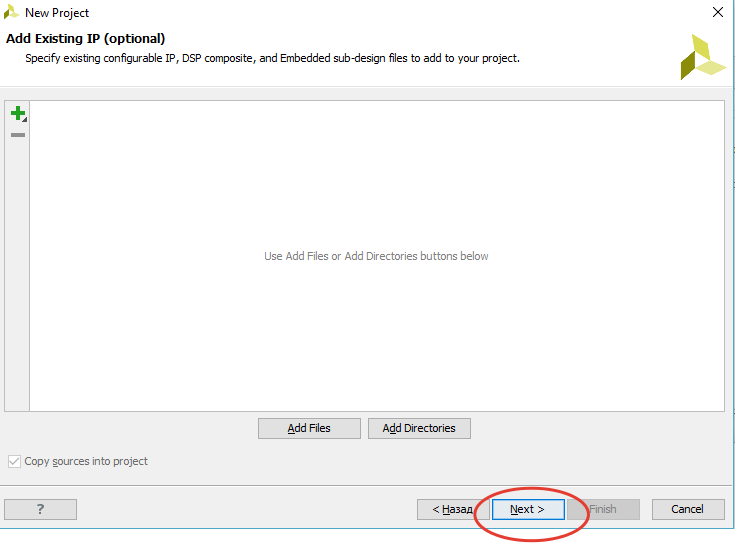

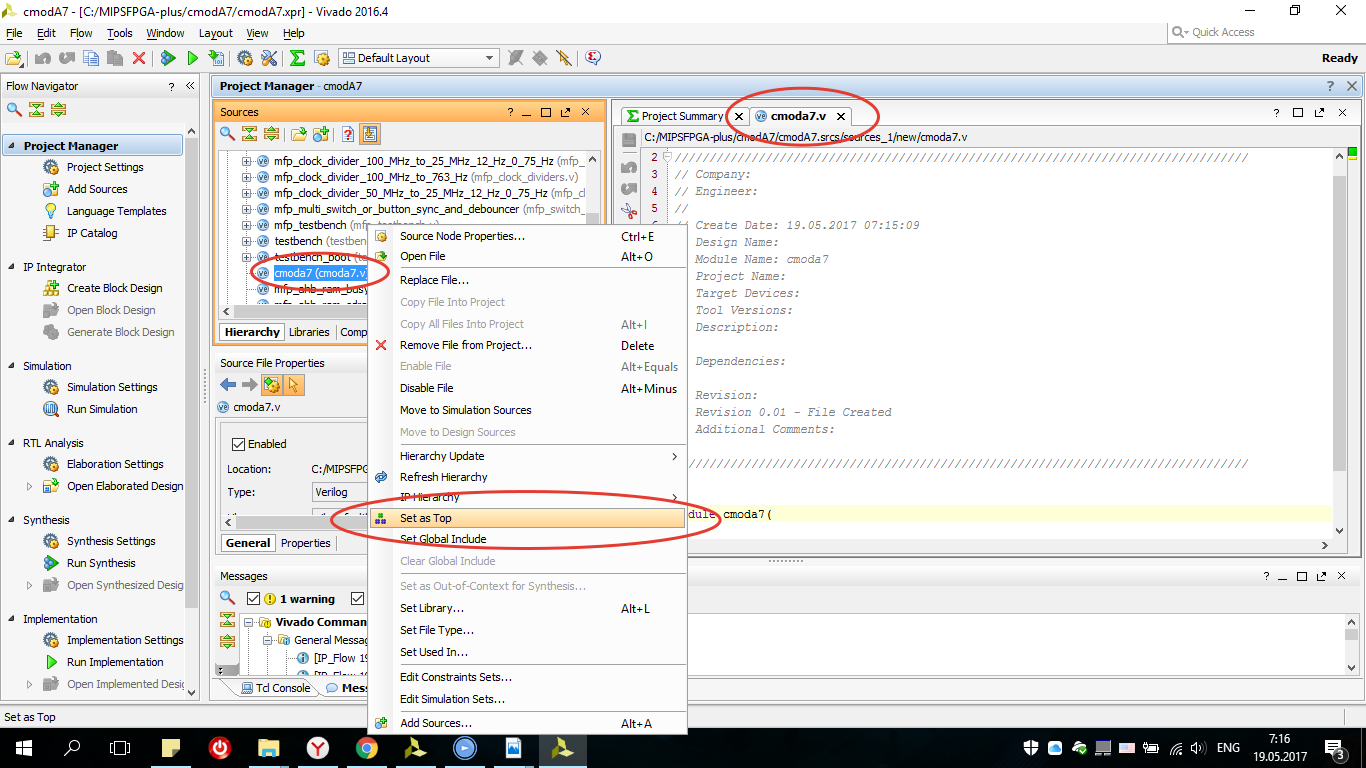

���������� �������� IP � ������ ����������� �������� �� �����:

����� ����� ���� ������� ���������� ���� �������� ���� �����.

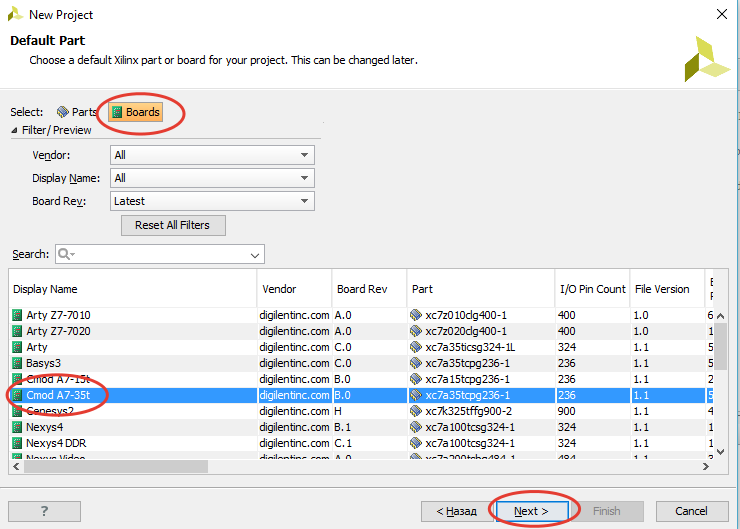

����� Digilent cmod A7 ���� ������� � ����� � �� �� ������� ����� � �������� ��� ������� �� ����� ����������. ����� ������� FPGA ����� ����� ��������� �� ���� ����� ������������, �� cmodA7 �������� ��� xc7a35tcpg236-1:

������ �������� �������� ���������� ����� ����� ����� � ���������� Vivado, ���� ������ ����� ��� ���, �� ������, ��������� �������� ����� ������� ��� ����, �� ������ ���� �� � ������� �������� ������������ block designer � Vivado, �� � ��� ����� �������������� �������������� ��� ������� ������ � ������������ �����, IP ������, � �.�. ������� �� ����� �� GitHub, ��������� ��� ����� ����� � ~\Vivado\2015.1\data\boards\ (��������� ��� Vivado 2015.1 � �����).

��� �� � ������� ������ � MIPSfpga-plus.

���������� �� ������������ �� ������� ����� Digilent CmodA7 �� ���� ���������� Artix-7

���� ������� �� �� ����� ����� cmodA7 ��������� ��� ��������� Artix-7, ����� 20800 LUT, 41600 FF, 225 KB ������� ������, ������� 48 �����, ����� ������� 2 �������� �������� ���, ����� ������� usb-uart ���������������, Quad-SPI Flash, � JTAG, 2 �������� ������, � ����� 5 ����������� 3 �� ������� ��� RGB (�������).

����� ��������� ������� MIPSfpga �� ����� cmodA7, �������:

��� 1. �������� ������-��������, ������� ������������� ������������ ����� �������/�������� MIPSfpga � �������/�������� ����� Basys3

��� 2. ��������� ����� ������ ������� MIPSfpga ��� ������������ ����� Basys3

��� 3. �������� ���� �����������, ������� ������������� ������������ ����� �������/�������� ����� � �������� ������� FPGA.

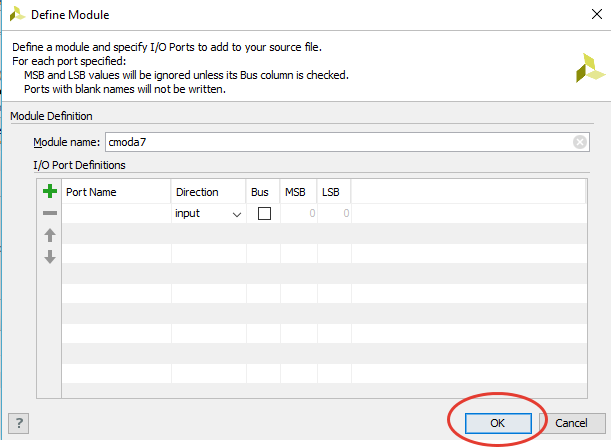

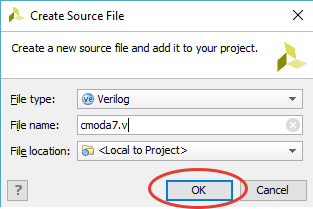

��� 1. ������� ����� ���� �������� cmoda7.v

��������� cmoda7.v ��� ������� � �������� �������.

��� ��� �� ����� cmoda7 ��� �������������� ������� ����� ���� �� ������������ ��� ��������� ������� ���������� (��� ����������� ��������� � MIPSfpga-plus), ���� ������ ������ �� ��� ������� � ������ ��������. ��� �� ����� ��������� ����� EJTAG � �������� ������������ BUS Blaster.

��� ������ ����� �������� ������������ ���� ������������ ���� AHB_lite.

`include "mfp_ahb_lite_matrix_config.vh"������������������� ���������������������� ���� (Advanced High-performance Bus, AHB) �������� �������� �����������, ������� ������������ �� ������ ����������������� ��������, �������� �� ����������. ���� AHB ��������� ����������� ���������� ���������� ���������. AHB-Lite �������� ���������� ������� AHB � ����� ������� �����������.

��� ������������ ����� ���� ������� ����������, ��������� MIPSfpga, � ��� �������: RAM0, RAM1 � GPIO, ������� ������������ ����� (��������������) ��� ����� ��� � ������ ������� � ����������� �����/������ �����. �� ��� ��� � ����� �������� � ������ GPIO � ������ ������ �������������� � ����������.

�������� �������� ����� �����-������:

module cmoda7

(

input i_clk,

input i_btn0,

input i_btn1,

input RsRx,

output [ 6:0] seg,

output dp,

output [ 3:0] an,

output led0_r,

output led0_g,

output led0_b,

inout [ 7:0] JA

);i_clk � ������ ��������� ���������� ����� �������� (��� cmodA7 12 ���).

i_btn0 � ������ ������������ ��� ������������ ����������.

i_btn1 � n/c.

RsRx � ������ ������ �� uart.

seg, dp, an, � �������� ��� ����������� ��������������� 4 ���������� ����������.

led_r, led_g, led_b, � ������ ������������ �� ����� RGB Led.

JA � Pmod ���������.

��������� ��������� �������� ������ �������� ������� � reset (i_btn0) ��������� ��� ����������� ���������.

�������� ����� ������ cmoda7.v �������� �������� ���������� ������� MIPSfpga-plus (mipsfpga_sys) � �� ���������� � �������/�������� �����.

wire clock;

wire reset = i_btn0;

wire display_clock;

wire [7:0] anodes;

wire [`MFP_N_BUTTONS - 1:0] IO_Buttons;

wire [`MFP_7_SEGMENT_HEX_WIDTH - 1:0] IO_7_SegmentHEX;

assign IO_Buttons = { { `MFP_N_BUTTONS - 2 { 1'b0 } } , i_btn0, i_btn1 };

mfp_system mfp_system

(

.SI_ClkIn ( clock ),

.SI_Reset ( reset ),

.HADDR ( ),

.HRDATA ( ),

.HWDATA ( ),

.HWRITE ( ),

.EJ_TRST_N_probe ( ),

.EJ_TDI ( ),

.EJ_TDO ( ),

.EJ_TMS ( ),

.EJ_TCK ( ),

.SI_ColdReset ( ),

.EJ_DINT ( 1'b0 ),

.IO_Switches ( ),

.IO_Buttons ( IO_Buttons ),

.IO_RedLEDs ( ),

.IO_GreenLEDs ( ),

.IO_7_SegmentHEX ( IO_7_SegmentHEX ),

`ifdef MFP_DEMO_LIGHT_SENSOR

.SPI_CS ( JA [0] ),

.SPI_SCK ( JA [3] ),

.SPI_SDO ( JA [2] ),

`endif

.UART_RX ( RsRx ),

.UART_TX ( )

);

`ifdef MFP_DEMO_LIGHT_SENSOR

assign JA [1] = 1'b0;

`endifMFP_DEMO_LIGHT_SENSOR ����� ������������ ��� ������������ ������������ �������. ��� ����� �� ������ ������� mfp_system ����� 32-� ��������� ���� IO_7_SegmentHEX ������� �� ������� � ������ ����������� 4-� ���������� 7 ����������� ����������, ��������� � �������� ������ ���������� �mfp_multi_digit_display�:

mfp_multi_digit_display multi_digit_display

(

.clock ( display_clock ),

.resetn ( ~ reset ),

.number ( IO_7_SegmentHEX ),

.seven_segments ( seg ),

.dot ( dp ),

.anodes ( an )

);��� �������� ����������� ����� ������ �������� �� ��������� � ����� ������ ��� �������.

��� ����������� ��������������� ���������� � ����� ������ ����� ����� ���:

module mfp_single_digit_seven_segment_display

(

input [3:0] digit,

output reg [6:0] seven_segments

);

always @*

case (digit)

'h0: seven_segments = 'b1000000; // a b c d e f g

'h1: seven_segments = 'b1111001;

'h2: seven_segments = 'b0100100; // --a--

'h3: seven_segments = 'b0110000; // | |

'h4: seven_segments = 'b0011001; // f b

'h5: seven_segments = 'b0010010; // | |

'h6: seven_segments = 'b0000010; // --g--

'h7: seven_segments = 'b1111000; // | |

'h8: seven_segments = 'b0000000; // e c

'h9: seven_segments = 'b0011000; // | |

'ha: seven_segments = 'b0001000; // --d--

'hb: seven_segments = 'b0000011;

'hc: seven_segments = 'b1000110;

'hd: seven_segments = 'b0100001;

'he: seven_segments = 'b0000110;

'hf: seven_segments = 'b0001110;

endcase

endmodule

//--------------------------------------------------------------------

module mfp_multi_digit_display

(

input clock,

input resetn,

input [31:0] number,

output reg [ 6:0] seven_segments,

output reg dot,

output reg [ 7:0] anodes

);

function [6:0] bcd_to_seg (input [3:0] bcd);

case (bcd)

'h0: bcd_to_seg = 'b1000000; // a b c d e f g

'h1: bcd_to_seg = 'b1111001;

'h2: bcd_to_seg = 'b0100100; // --a--

'h3: bcd_to_seg = 'b0110000; // | |

'h4: bcd_to_seg = 'b0011001; // f b

'h5: bcd_to_seg = 'b0010010; // | |

'h6: bcd_to_seg = 'b0000010; // --g--

'h7: bcd_to_seg = 'b1111000; // | |

'h8: bcd_to_seg = 'b0000000; // e c

'h9: bcd_to_seg = 'b0010000; // | |

'ha: bcd_to_seg = 'b0001000; // --d--

'hb: bcd_to_seg = 'b0000011;

'hc: bcd_to_seg = 'b1000110;

'hd: bcd_to_seg = 'b0100001;

'he: bcd_to_seg = 'b0000110;

'hf: bcd_to_seg = 'b0001110;

endcase

endfunction

reg [2:0] i;

always @ (posedge clock or negedge resetn)

begin

if (! resetn)

begin

seven_segments <= bcd_to_seg (0);

dot <= 0;

anodes <= 8'b00000001;

i <= 0;

end

else

begin

seven_segments <= bcd_to_seg (number [i * 4 +: 4]);

dot <= 0;

anodes <= (1 << i);

i <= i + 1;

end

end

endmodule

��� ����� ������� �� ������� ��������� ������ clock � seven_segments ��������� ��������������� ������ bcd_to_seg, � ������������ ����� ��������� ���������� ������������ � ������� ������������ ��������� ������� �� ��������������� ������ (���� �������).

��� ��� �� ���� ���������� ��������� ������ � �������� � 50 ��� ������� �� �������� �����, ���� �� ����� � ����� �������� ������ �������� �� ���������� ��� ���� �� ����� �������� ��� ���������(��� ����������� ����������� �������� �� 7 ���������� ���������� ���������� ������� �������������� � 763 ��). ��� ����� ��������� ��������� �������� �������:

mfp_clock_divider_50_MHz_to_763_Hz mfp_clock_divider_50_MHz_to_763_Hz

(clock, display_clock);� �������� ������ �������� ������� � 50 M�� � 763 �� ���. ������� �� ������� ��� � ���� mfp_clock_dividers.v:

module mfp_clock_divider_50_MHz_to_763_Hz

(

input clki,

output clko

);

mfp_clock_divider

# (.DIV_POW_SLOWEST (16))

mfp_clock_divider

(

.clki ( clki ),

.sel_lo ( 1'b1 ),

.sel_mid ( 1'b0 ),

.clko ( clko )

);

endmodule

�� ���� ������� ��������� ������� reset � clock, RsRx, IO_Buttons. �� � ��� �� ����� ��� ������ ������ i_clk, � �� clock. ���� � ��� ��� �� ����� ������������ �������� ��������� � 12 ���, � ��������� � FPGA ����� �������� �� �������� 50 ��� � ����, � ��� ������ ���� � ��� ������ ����� � ������ �������� �������� (�������� Nexys 4 DDR ����� �������� ������� 100 ���). �������� �������� ��������� IP ���� Clocking Wizard (PLL), ��� ����� ������� IP �������:

������� Clocking Wizard:

������� board ��������� ��� ����, ���� ����������� ������ ��� ����� � ��������� �� ������� clocking options ����� ������� ���� MMCM ����� ����� ������� �������� ������� ������ 10...800���, ��� PLL 19...800���, ��������� �� cmoda7 ����� 12 ��� �������� MMCM, �� ��� ������ ���� ����� �������� ������ ���������:

�� ������� output clocks ������������� ������� 50 ��� (� �������� ����� � ����� ������������������, ��� �� ������ FPGA ����� ���� ������ ��������������):

����� ������� reset � locked:

Port renaming, MMCM setting � Summary ������� � ��������� ��� ����, ���� ��, ��, � ��������� ���� �������� generate:

��������� ������� ������� ����������� ������������ ��� RGB Led, ��������� ��� ����� �� ����� � ��������� ��������� ��� ����� ������ ��������, � �� ����� ��� �� ��� ���� ���������:

assign led0_r = 1'b1;

assign led0_g = 1'b1;

assign led0_b = 1'b1;� ����� �������:

endmodule������ �������� ������, �������� � ��������� ������� ������.

��� 2. ��������� ����� ������ ������� MIPSfpga ��� ������������ ����� cmoda7

����� cmoda7 ����� 225 ����� �������� ������. ����� �������, ��� ����� ������ (128 ����� ��� ������ � 256 ����� ��� ��������) �� ���������� �� ����� cmoda7. ��� ���, ����������� ��� ����� ���������� � 32 �����, � ����� ���������� ����������� �������� ������� 64 �����. ����� �������, ����� ����������� ������ (32 K���� + 64 K���� = 96 K����) ������������� ������ ������ ����� cmoda7. ���������� 225-96 = 129 K���� ������ ����� ���� ������������ ��� ������ ���� ������� MIPSfpga, ��������, � �������� ���-������.

��������� ����� ������ �����, ������� ������ ������, ���������� � ������������ ����� Verilog ������� �� ���������� � ���� �������� �mfp_ahb_lite_matrix_config.vh�. ��������� ���� mipsfpga_ahb_const.vh. ������ ��� ������ (��� ��� ��������) ������� �� 13 ���. ����� �������, ����� ��� ������ ����� 213 32-������ ���� = 215 ���� = 32 K����.

`define H_RAM_RESET_ADDR_WIDTH 13 ������ ��� �������� ������� �� 14 ���. ����� �������, ����� ��� �������� ����� 214 32-������ ���� = 216 ���� = 64 K����.

`define H_RAM_ADDR_WIDTH 14��� 3. ������� ���� ����������� cmoda7

������ �������� �cmoda7.xdc� ������� ������������� ������������ ����� �������� ��������� ������-�������� � �������� ������� FPGA ����� cmoda7 (xdc ���� � ������ ������� ������� ��� cmoda7):

## Clock signal 12 MHz

set_property -dict {PACKAGE_PIN L17 IOSTANDARD LVCMOS33} [get_ports i_clk]

create_clock -period 83.330 -name sys_clk_pin -waveform {0.000 41.660} -add [get_ports i_clk]

## Buttons

set_property -dict {PACKAGE_PIN A18 IOSTANDARD LVCMOS33} [get_ports i_btn0]

set_property -dict {PACKAGE_PIN B18 IOSTANDARD LVCMOS33} [get_ports i_btn1]

## LEDs

set_property -dict {PACKAGE_PIN B17 IOSTANDARD LVCMOS33} [get_ports led0_b]

set_property -dict {PACKAGE_PIN B16 IOSTANDARD LVCMOS33} [get_ports led0_g]

set_property -dict {PACKAGE_PIN C17 IOSTANDARD LVCMOS33} [get_ports led0_r]

## Pmod Header JA

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {JA[0]}]

set_property -dict {PACKAGE_PIN G19 IOSTANDARD LVCMOS33} [get_ports {JA[1]}]

set_property -dict {PACKAGE_PIN N18 IOSTANDARD LVCMOS33} [get_ports {JA[2]}]

set_property -dict {PACKAGE_PIN L18 IOSTANDARD LVCMOS33} [get_ports {JA[3]}]

set_property -dict {PACKAGE_PIN H17 IOSTANDARD LVCMOS33} [get_ports {JA[4]}]

set_property -dict {PACKAGE_PIN H19 IOSTANDARD LVCMOS33} [get_ports {JA[5]}]

set_property -dict {PACKAGE_PIN J19 IOSTANDARD LVCMOS33} [get_ports {JA[6]}]

set_property -dict {PACKAGE_PIN K18 IOSTANDARD LVCMOS33} [get_ports {JA[7]}]

## GPIO Pins 1 - 6 7_segment_ind

set_property -dict {PACKAGE_PIN M3 IOSTANDARD LVCMOS33} [get_ports {seg[1]}]

set_property -dict {PACKAGE_PIN L3 IOSTANDARD LVCMOS33} [get_ports {an[1]} ]

set_property -dict {PACKAGE_PIN A16 IOSTANDARD LVCMOS33}[get_ports {an[2]} ]

set_property -dict {PACKAGE_PIN K3 IOSTANDARD LVCMOS33} [get_ports {seg[5]}]

set_property -dict {PACKAGE_PIN C15 IOSTANDARD LVCMOS33}[get_ports {seg[0]}]

set_property -dict {PACKAGE_PIN H1 IOSTANDARD LVCMOS33} [get_ports {an[3]} ]

## GPIO Pins 43 - 48 7_segment_ind

set_property -dict {PACKAGE_PIN U3 IOSTANDARD LVCMOS33} [get_ports {seg[3]}]

set_property -dict {PACKAGE_PIN W6 IOSTANDARD LVCMOS33} [get_ports {seg[4]}]

set_property -dict {PACKAGE_PIN U7 IOSTANDARD LVCMOS33} [get_ports dp ]

set_property -dict {PACKAGE_PIN W7 IOSTANDARD LVCMOS33} [get_ports {seg[2]}]

set_property -dict {PACKAGE_PIN U8 IOSTANDARD LVCMOS33} [get_ports {seg[6]}]

set_property -dict {PACKAGE_PIN V8 IOSTANDARD LVCMOS33} [get_ports {an[0]} ]

## UART

#set_property -dict { PACKAGE_PIN J18 IOSTANDARD LVCMOS33 } [get_ports { uart_rxd_out }]; #IO_L7N_T1_D10_14 Sch=uart_rxd_out

set_property -dict {PACKAGE_PIN J17 IOSTANDARD LVCMOS33} [get_ports RsRx]

��������, ��������� ������ ������������� ������������ ����� ������ i_clk � ������� ������� FPGA L17, �� ������� ��������� �������� ������ � �������� 12 ��� � ����� cmoda7.

set_property -dict {PACKAGE_PIN L17 IOSTANDARD LVCMOS33} [get_ports i_clk]

create_clock -period 83.330 -name sys_clk_pin -waveform {0.000 41.660} -add [get_ports i_clk]��� �� � ���� ����������� ����� �������� ��������� �������� ��������� ����������� ��� ��������:

# I/O virtual clock

create_clock -period 83.330 -name "clk_virt"

# tsu/th constraints

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports i_btn0]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports i_btn0]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports i_btn1]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports i_btn1]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports led0_b]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports led0_b]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports led0_g]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports led0_g]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports led0_r]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports led0_r]

## PMOD ALS

set_output_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {JA[0]}]

set_output_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {JA[0]}]

set_output_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {JA[1]}]

set_output_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {JA[1]}]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {JA[2]}]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {JA[2]}]

set_output_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {JA[3]}]

set_output_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {JA[3]}]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {seg[]}]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {seg[]}]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports {an[]}]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports {an[]}]

set_input_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports dp]

set_input_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports dp]

set_output_delay -clock "clk_virt" -min -add_delay 0.000 [get_ports RsRx]

set_output_delay -clock "clk_virt" -max -add_delay 10.000 [get_ports RsRx]���� MIPSfpga

�� ����� �������������� ������������ �� ���� ����� ���������, ��� ����� ����� ����� � ���� ������������ �mfp_ahb_lite_matrix_config.vh� � ��������������� ������:

`define MFP_DEMO_LIGHT_SENSOR

����� ������� �� ���������� ���������� �� Verilog ������ ���������� SPI � ���� AHB Lite ��� ���������� � �������� ������������ PmodALS ����� Digilent.

������ SPI

module mfp_pmod_als_spi_receiver

(

input clock,

input reset_n,

output cs,

output sck,

input sdo,

output reg [15:0] value

);

reg [21:0] cnt;

reg [15:0] shift;

always @ (posedge clock or negedge reset_n)

begin

if (! reset_n)

cnt <= 22'b100;

else

cnt <= cnt + 22'b1;

end

assign sck = ~ cnt [3];

assign cs = cnt [8];

wire sample_bit = ( cs == 1'b0 && cnt [3:0] == 4'b1111 );

wire value_done = ( cnt [21:0] == 22'b0 );

always @ (posedge clock or negedge reset_n)

begin

if (! reset_n)

begin

shift <= 16'h0000;

value <= 16'h0000;

end

else if (sample_bit)

begin

shift <= (shift << 1) | sdo;

end

else if (value_done)

begin

value <= shift;

end

end

endmodule

����� ����������� ���������� �� �������:

������ ��������� � ����� Pmod, ������ �������� ������� � �cmoda7.xdc� ��������� ��� JA[7..0].

## Pmod Header JA

set_property -dict {PACKAGE_PIN G17 IOSTANDARD LVCMOS33} [get_ports {JA[0]}]

...

set_property -dict {PACKAGE_PIN K18 IOSTANDARD LVCMOS33} [get_ports {JA[7]}]��������� RTL ����� ����� ��������� �� ������� RTL Analisys -> Schematic, ��� ������ ���������� SPI �mfp_pmod_als_spi_receiver� ��������� � �mfp_system�:

��� �� ��������� � FPGA ��������� ������ ����� ������������� bitstream ���� �cmoda7.bit�, ��� ����� �� ������� Program and Debug -> Generate Bitstream � ��������� ���������� ��������:

����� �������� bitstream ����� ����� ��� ��������� � �����, ��� ����� �� ������� Program and Debug -> ������� Open Hardware Manager -> Open Target -> Auto Connect -> Program Device � �������� �������:

�������� ��������� ��� ������ � ��������

����� ��������� ����������� � �������� ������� ����� �������� ��������� � ��������� � ���� RAM1 ������� ��� �� ��������� � ���� AHB Lite.

��������� MIPSfpga ������������� � �������������� ������������ ���������� Codescape �������� Imagination. ���������� Codescape SDK � OpenOCD. Codescape ������������ ���������������� ��� �� ����� C, ��� � �� ����� ����������.

��� �������� ���� � ������� ����� ������� � ����� ��������� mipsfpga plus -> github -> mipsfpga-plus -> programs-> 01_light_sensor ������� �mfp_memory_mapped_registers.h�.

#define MFP_LIGHT_SENSOR_ADDR 0xBF800014

�

#define MFP_LIGHT_SENSOR (* (volatile unsigned *) MFP_LIGHT_SENSOR_ADDR )

����� ������� main.c � ������� ���� �����:

#include "mfp_memory_mapped_registers.h"

int main ()

{

int n = 0;

for (;;)

{

MFP_7_SEGMENT_HEX = MFP_LIGHT_SENSOR;

}

return 0;

}

����� � ����� ������� ������ ������� ����������� ���:

02_compile_and_link���������� motorola_s_record ����:

08_generate_motorola_s_record_file��������� � ������ ��� ����� ��������� USB UART ���������������:

11_check_which_com_port_is_used�������� ���� 12_upload_to_the_board_using_uart:

set a=7

mode com%a% baud=115200 parity=n data=8 stop=1 to=off xon=off odsr=off octs=off dtr=off rts=off idsr=off type program.rec >\.\COM%a%��� � � ����� ��� �����, � �������� ��������� USB UART ���������������. � ��������� ���������:

12_upload_to_the_board_using_uart��������� ������������ ������� ����� ���������� �� �����:

��� ��������� ������ ����������, � ����������� ��������� ����� ������� �� ����� �������� ���������� (Verilog, VHDL), � ��� �� ������������, ����������� ����������, ���������������� (����������� ������������� ���������) � ���������������� �� ����������, � ����� ���� ������� ��� ������� ��� ����� ����� � �������� ����� ��� ������� � ������������ ������������� ��������� ����� ��� ������� �������� � ������: ���������� ������� �����������, ����������� ���������� � ��������������� ���������������� �� ������� �����.

� ��������� ����� ����� ������� ��� ���������� ��������� ��������� � ������� MIPSfpga �� ������� ���������� Digilent Pmod KYPD, ���������� ���, � LCD ������� �� Nokia.

| �������������� | « ����. ������ — � �������� — ����. ������ » | ��������: [1] [�����] |