Добавить любой RSS - источник (включая журнал LiveJournal) в свою ленту друзей вы можете на странице синдикации.

Исходная информация - http://panchul.livejournal.com/.

Данный дневник сформирован из открытого RSS-источника по адресу http://panchul.livejournal.com/data/rss/, и дополняется в соответствии с дополнением данного источника. Он может не соответствовать содержимому оригинальной страницы. Трансляция создана автоматически по запросу читателей этой RSS ленты.

По всем вопросам о работе данного сервиса обращаться со страницы контактной информации.

[Обновить трансляцию]

Что делать, когда выпускник топ-10 мирового вуза не может спроектировать блок сложения A+B |

У меня был в свое время практикант из Стенфорда, от которого я получил инсайдерскую информацию, чему их там учат. Потом я интервьировал много студентов, и понял, что если человек не делает самостоятельных проектов в вузе, а просто плывет по течению программы как медуза, то будучи выброшенным на берег индустрии, он становится совершенно беспомощным.

Когда я вижу у недавнего выпускника в резюме какой-то из протоколов в котором используется valid/ready, например AXI или AHB, я прошу его спроектировать блок, у которого на входе два числа A и B, а на выходе их сумма. Разумеется не просто написать SUM=A+B, а еще и поставить valid/ready сигналы на каждый из A, B, SUM, чтобы A и B могли приходить в разное время, а также чтобы блок ждал, если SUM не может быть передана другому блоку сразу.

Некоторые не справляются. Грустно смотреть на человека, который потратил 6 лет своей жизни (4 года в бакалавриате и 2 года в магистратуре) и океан денег на образование – и не может сложить два числа и бьется как угорь на сковородке. То блок не работает когда числа приходят в разное время, то создатель забывает снять valid, и блок на 2+2 выдает не 4, а 4-4-4-4-4-4-4… То числа складываются не попарно, а просто записываются в регистры и на выход идет их текущая сумма, хотя количество аргументов A и B не совпадает. То не отрабатывается backpressure и результаты теряются, то (после того как кандидат написал страницу кода на верилоге) блок работает на половинной производительности, то есть не может принимать поток чисел подряд, а ожидает между ними пропуски (gaps). Короче ведет себя как ChatGPT.

Конечно, если студент сам во время учебы делает скажем правильные open-source проекты, то он вписывается в индустрию легче. Но все равно компании тратят много усилий на переподготовку недавних студентов. Некоторые электронные компании нанимают профессиональных тренеров типа Клифа Каммингса, которые берут три тысячи долларов за неделю трейнинга за_каждого_студента.

Я в свое время пытался привезти Клиффа в Россию, но в первую попытку звезды не сошлись (хотя все топ российские электронные компании согласились прислать по одному-два инженера). А во второй раз настала международная напряженность и все накрылось – Клифф продал свою компанию бОльшей трейнинг-компании и там менеджер не захотел.

Я это все к чему – я на днях прочитал на Хабре что Ядро/Syntacore решили сделать целый внутренний курс для тренировки ASIC проектировщиков из бывших FPGA проектировщиков:

Это в принципе крутая идея, так как отличия front-end ASIC от FPGA инженеров не такие уж большие:

- FPGA инженер с опытом мою задачку про A+B решит.

- В FPGA как правило менее навороченные микроархитектуры, чем в ASIC, но это дело количественное, а не качественное в смысле опыта.

- В ASIC есть больше всякого self-теста, scan chains, энергопотребления – но это в основном забота physical design teams, а не front-end designers.

Замечу что Элон Маск в свой SpaceX сейчас интервьирует на смешанную ASIC/FPGA позицию:

Но что делать тем, кто еще не готов идти в Ядро/Syntacore и хочет натренировать себя в FPGA? Предположим, что у вас есть некий начальный опыт, например почерпнутый из источников, которые я перечислил в презентации для проектов в Средней Азии, курса в ВШЭ МИЭМ или скажем по ссылкам из телеграм-каналов fpgasystems , tinyurl.com/yy79xfer, DigitalDesignSchool , сайта ранних энтузиастов FPGA в России marsohod.org итд:

Следующий шаг – набрать опыта на открытых проектах, и у меня как раз есть такой проект, для которого я собираю команду. Это проект YRV-Plus, см. поддерево Plus в репозитории github.com/yuri-panchul/yrv-plus . Суть проекта – накрутить опций вокруг RISC-V ядра микроконтроллерного класса под названием YRV. В том числе:

- Запустить ядро YRV на дюжине FPGA плат от Altera / IntelFPGA, Gowin, Xilinx, Lattice.

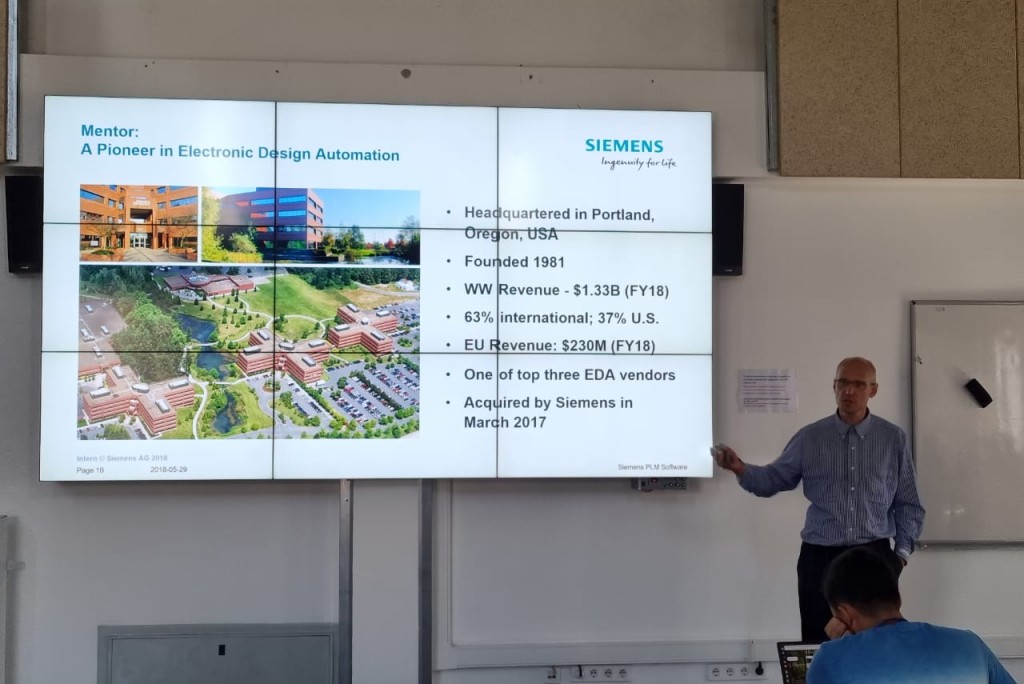

- Сделать скрипты для работы YRV на различных симуляторах: Synopsys VCS, Cadence Xcelium, Siemens EDA / Mentor Questa, Icarus Verilog, Verilator.

- Сделать пару десятков интересных софтверных примеров на ассемблере, в частности с обработкой прерываний.

- Сделать различные варианты linker script для компиляции софтверных примеров на Си.

- Сделать пример разделения общей памяти между тремя такими ядрами. Сделать разделяемую память многобанковой и показать, как количество банков влияет на производительность.

- Сделать пример обмена сообщениями между несколькими ядрами с помощью так называемого gated storage. Одно ядро пишет, а другое читает из адреса, который отображается не на обычную память, а на очередь FIFO. Когда FIFO наполнено, записывающее ядро останавливается на следущей записи. Когда FIFO пустое, читающее ядро останавливается на следующем чтении.Показать изменение производительности в зависимости от глубины FIFO и поведения программ.

- Сделать контроллер SDRAM памяти для разных плат и интегрировать его с YRV.

- Присоединить к ядру различные кэши: полностью ассоциативные, прямого отображения, многосекционные, с различными стратегиями замещения. Показать изменение производительности с различными сценариями доступа к данным.

- Спортировать на YRV какой-нибудь бесплатный RTOS, например FreeRTOS.

- Реализовать в ядре FPU и сравнить его производительность по сравнению с библиотечно-целочисленной реализацией плавающей арифметики (начать со сложения или умножения). Сравнить размер и максимальную тактовую частоту получившихся ядер.

- Реализовать в ядре векторые расширения и продемонстрировать, какое они дают увеличение производительности.

- Присоединить к ядру сопроцессор для работы с графикой, чтобы с ним можно было сделать учебную игровую приставку.

- Измерить производительность ядра YRV на бенчмарках Dhrystone и CoreMark, сравнить с другими открытыми ядрами, в частности: Syntacore SCR1, ядро mirisc от Московского института электронной техники и SweRV EH1 от Western Digital.

- Верифицировать ядро с различными наборами тестов.

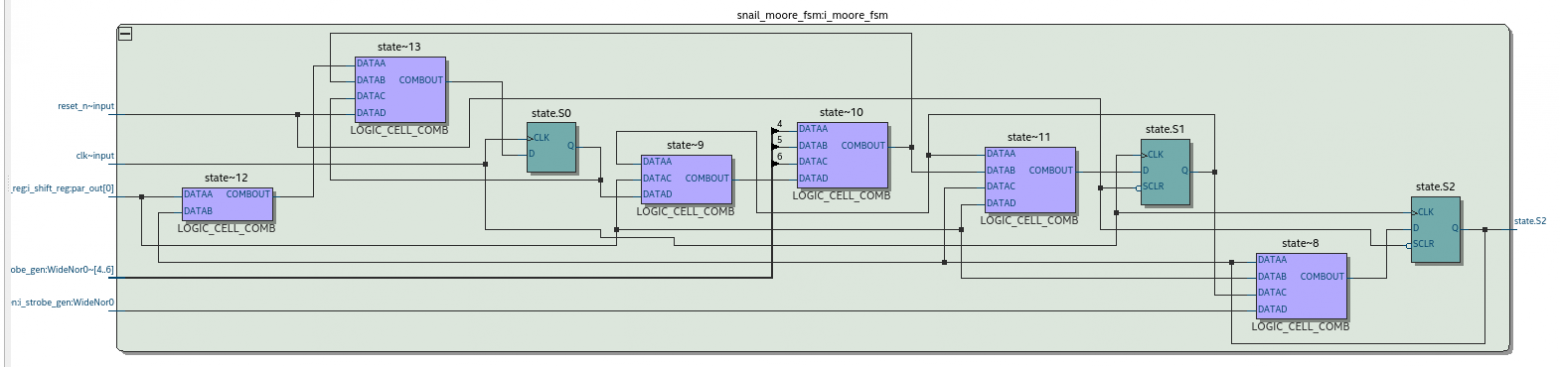

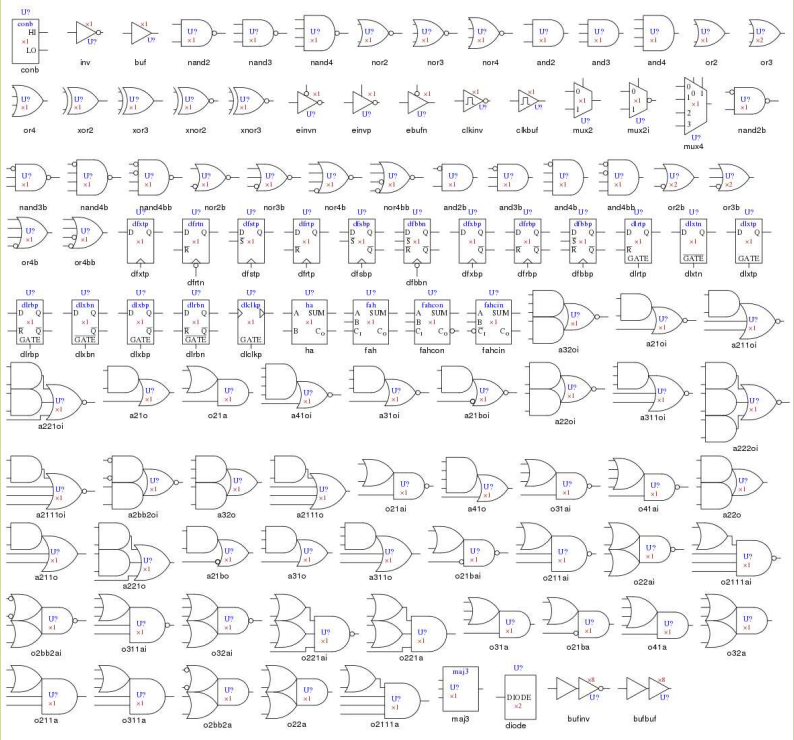

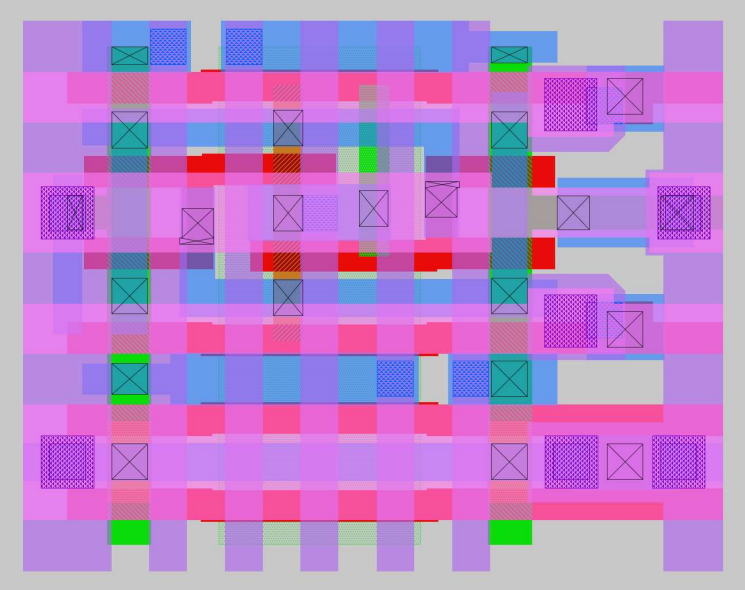

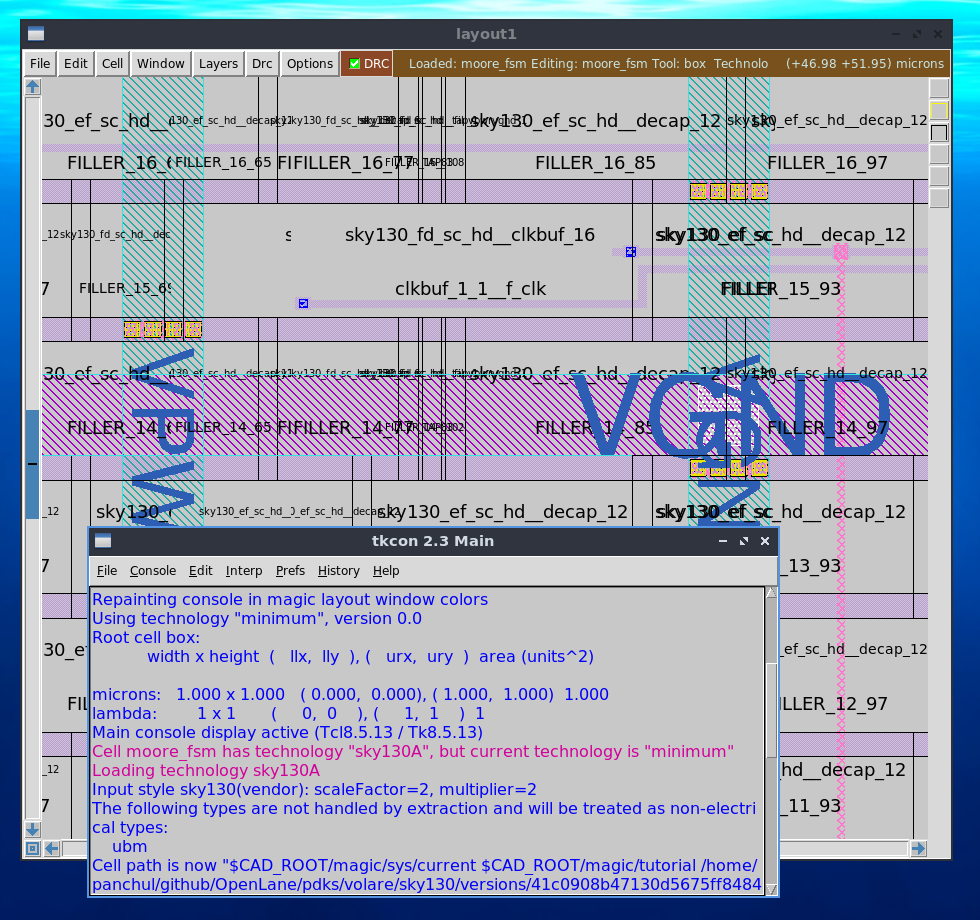

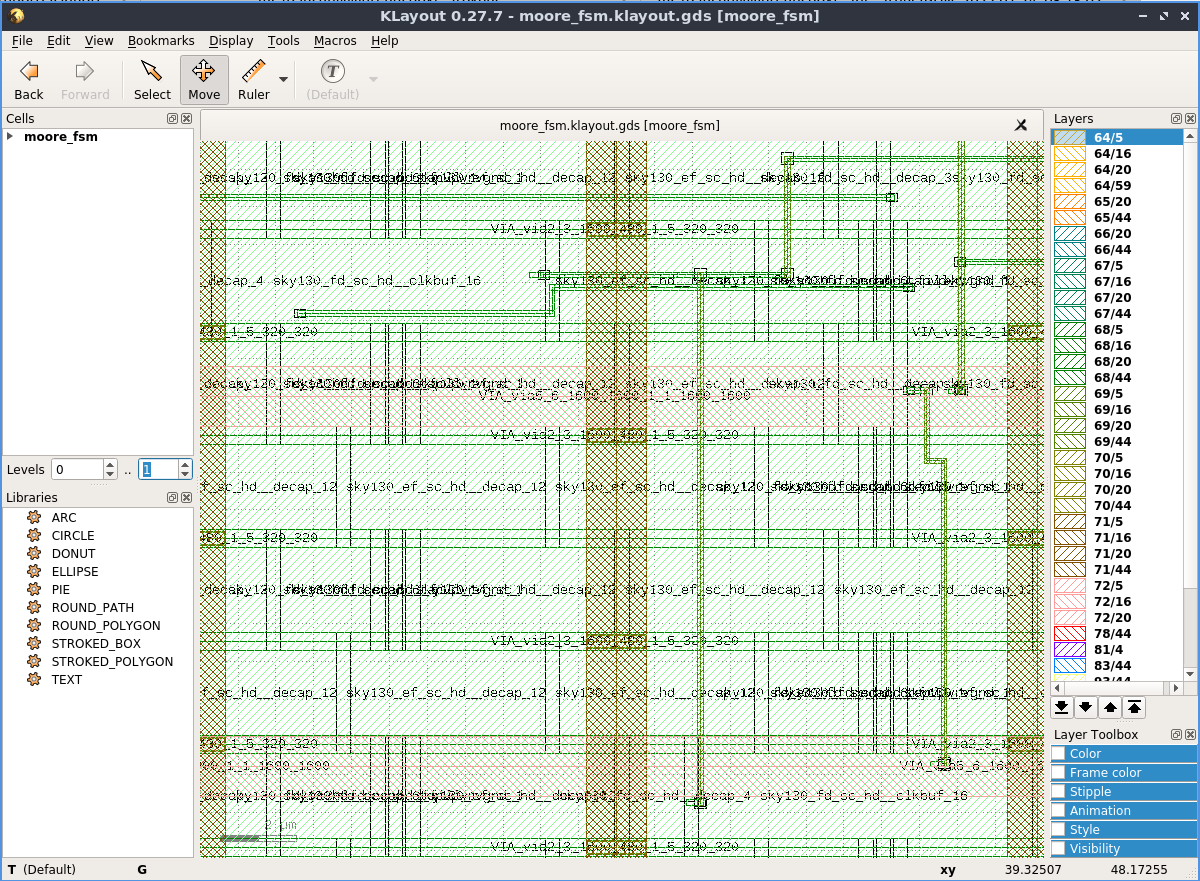

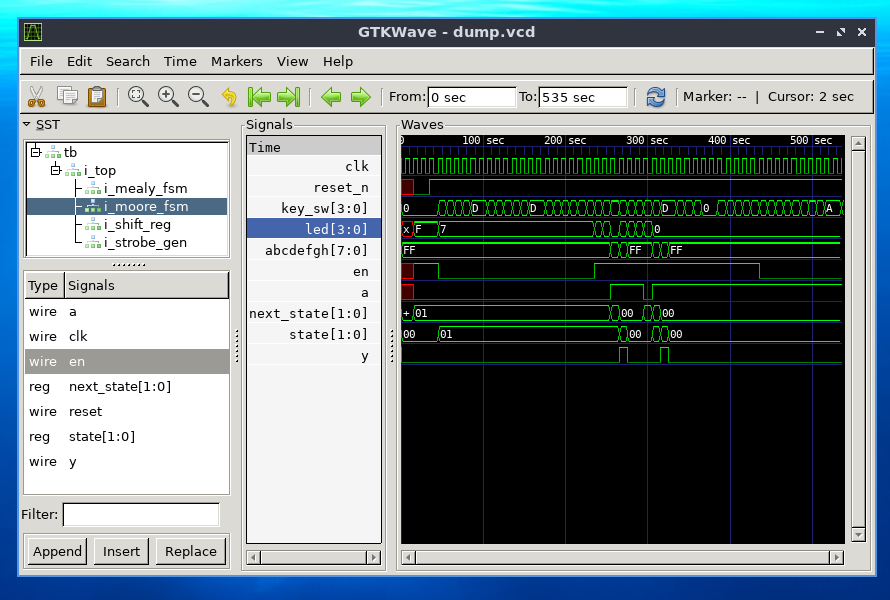

- Синтезировать YRV для ASIC с помощью открытого маршрута Open Lane и System-on-Chip (SoC) платформы Caravel. Вот тут-то вы можете начать переучиваться на ASIC.

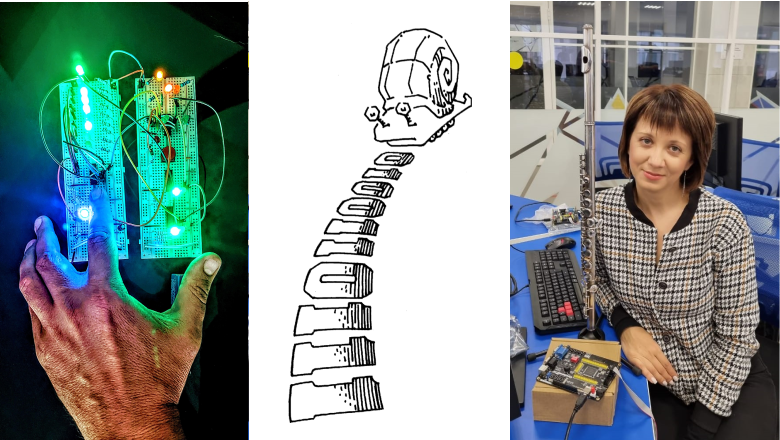

В частности нужно спортировать YRV на плату Tang Primer 20K c китайским GoWwin FPGA, с которой на фотографии слева работает мой приятель Александр Белиц, инженер из компании Marwell. Эта плата недорогая и вместительная, использует систему разработки от GoWin, которая является альтернативой Intel FPGA Quartus и Xilinx Vivado.

Также в частности стоит спортировать YRV на плату Digilent Nexys4 DDR, которую держит в руках девушка Ирина из Новосибирского Академгородка. Эту плату с системой разработки Xilinx Vivado используют большое количество вузов.

Почему именно процессорное ядро YRV, хотя вокруг этих RISC-V ядер немерянное количество? По комбинации факторов:

- YRV одновременно является полнофункциональным RISC-V ядром (не учебным подможеством), и при этом имеет очень компактный размер, то есть влазит в недорогие FPGA платы.

- YRV написал проектировщик Монте Далримпл, который занимается процессорами с 1970-х годов в компании Zilog, использует Verilog с начала 1990-х годов, спроектировал кучу чипов, в том числе для космоса. То есть это в чистом виде “старый конь борозды не испортит” – Монте чувствует тайминг, пишет все аккуратно и читабельно, понимает какая нужна периферия и контроллер прерываний для микроконтроллера.

- Монте все задокументировал в собственной книжке, которая также описывает весь материал по архитектуре RISC-V необходимый для работы с его процессорным ядром:

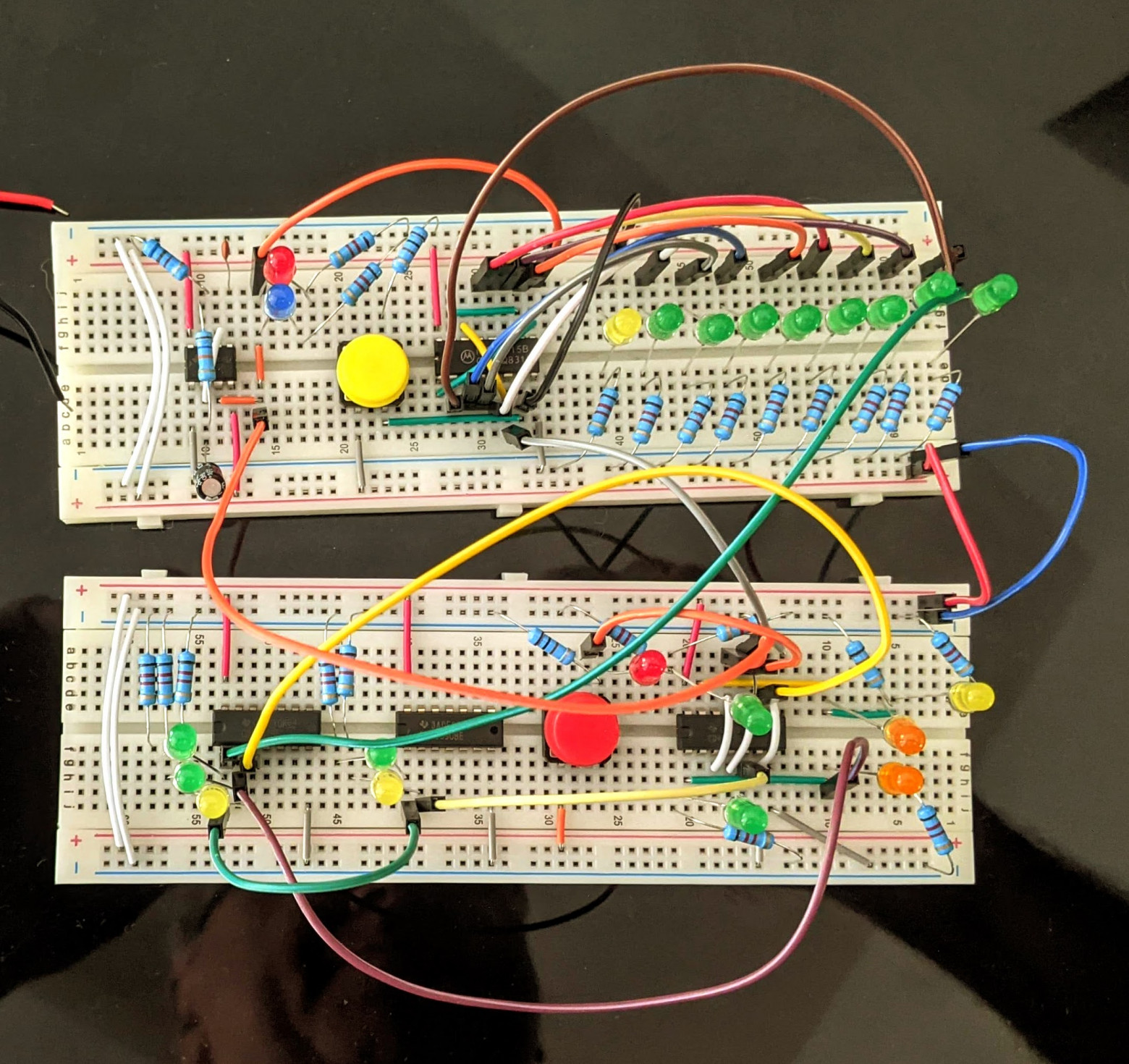

К нашей open-source команде, помимо Монте, меня и Белица, присоединился Дмитрий Петренко. Дмитрий одолжил несколько альтеровских плат от программы одалживания FPGA плат Михаила Коробкова и перенес на них YRV. Также Дмитрий написал линкер-скрипт и смог построить маршрут писания программ для YRV на Си (hello world). Вот платы Дмитрия в работе:

Мы недавно с Александром Белицем обедали с Монте Делримплом в Ливерморе, городе, который был недавно в новостях по поводу термояда. Монте там живет. В центре города стоит скульптура – вращающийся шар с фонтаном и надписями про российcко-американское сотрудничество в физике. Кстати по странам происхождения четыре участника проекта являются выходцами из четырех стран – России, Украины, Белоруссии и США – угадайте кто откуда.

Так что присоединяйтесь пятым и более. Репозиторию можете форкнуть у меня или у Дмитрия (ссылка выше). Мы проводим еженедельные созвоны в 9 утра в воскресенье по Калифорнии (это 20.00 вечера воскресенье по Москве).

Но если вы уже изучили простые процессоры и основы FPGA, присоединяйтесь сразу к Ядру/Syntacore . Если нет – можете еще пройти курс лабораторных от МИЭТ по проектированию однотактного процессора с прерываниями и периферией (видео их лекций). И потом присоединиться к новому проекту MIRISC в МИЭТ с более сложным конвейером. Это ситуация “пусть цветут все цветы, заимствуют и меряются друг с другом”

|

|

Камерон о поставке оружия на Украину, опухоль мозга у принца Британии и другие фейки от ChatGPT |

ChatGPT давно заслужил помещение в Миротворец. Хотите сгенерировать речь Зеленского в российской Госдуме с предложением Крыма в обмен на мир? Этого вам ChatGPT сделать не даст, так как в нем стоит блокировка обсуждения Крыма, но если заменить слово «Крым» словосочетанием «территориальные концессии», то ChatGPT генерит речь на «ура».

Готовы к реальному хардкору? Как насчет связать рак мозга в британской королевской семье с проблемой украинских беженцев в Европе? Да ни вопрос!

Но начнем с чего-нибудь более нейтрального. ChatGPT, сгенери речь режиссера фильма Аватар к Конгрессу США с просьбой остановить поставку оружия Украине. А также (второй вариант) с призывом увеличить поставки:

Хорошо, как насчет того же самого от автора теории «конца истории» Фрэнсиса Фукуямы? «Вжик» — сказала электропила (если вы знаете этот анекдот):

А что если вложить это в уста президента Японии и для обоснования взять популярную во времена пика «японского чуда» книжку «Япония может сказать Нет!»? Да ни вопрос, банзай как говорится:

Прибавить немного цинизма? Ну ОК:

Сделать это троллическим и именем короля? Пожалуйста:

Что же ChatGPT не разрешает? Помимо обсуждения Крыма он не разрешает сочинять речи для Путина. Но не против, если заказать историю о Майдане от солдата ДНР. Правда в эту историю, как ни перекручивать запрос, будет вставляться ровно одна однобитовая манихейская трактовка Добра и Зла. Что показывает, что политоту в ChatGPT вбили ручками, а не просеиванием через него петабайтов данных из интернета.

Ну и напоследок — обещанная история про принца. Просто помещая в один абзац тяжелые заболевания, британскую королевскую семью и Украину, можно автоматически генерить годную тролятину для интернет-хомячков:

Правильно сказал комментатор в The Verge, что нужно нанять «реальных американцев» которые бы ограждали общество от этого:

|

|

День Рождения 2022 |

|

|

AI как угроза удаленным собеседованиям на работу. ChatGPT = CheatGPT? |

У меня по всей френдленте идут хиханьки-хаханьки про ChatGPT - одни восторгаются ее гениальностью, а другие тупостью. А вот я вчера осознал стремную вещь - вероятно ChatGPT уже стали использовать во время удаленных интервью на работу. Просто я дал ChatGPT тот же вопрос, который я задал кандидату во время недавнего интервью, и ChatGPT сгенерил мне код с теми же ошибками - сделал upstream ready не output, а input например, потом сделал код с gap-ами на входе, а потом просто слил, заявив что слишком много запросов.

У меня недостаточно информации для обсуждения природы GPT. В него за 6 лет вложили миллиарды и один из участников - это компания в Индии с большим количеством программистов. То есть они могли экстенсивно натаскать программу на простые вопросы типа "напиши код для декодера" и их комбинации "напиши мультплексор как комбинацию декодера и селектора". Легко угадать, что куча людей будут пытаться сбивать GPT запросами про редкие языки программирования (Algol-60, ABEL) и можно прикинуться ветошью если языка не знаешь (на мой запрос написать нечто на Snobol-4 GPT стал писать на Algol-60). В сложных вопросах GPT ведет себя как Eliza 1964-го года (см. вопрос про конвейерный PDP-11 с автоинкрементной адресацией).

Но во всем этом хайпе есть важная практическая часть, которую стоит учесть немедленно. На интервью через zoom больше нельзя давать кандидатам воспросы, на которые "на троечку" может ответить GPT, запущенная в соседнем окне. В принципе, от кандидатов можно требовать написать к собственному ответу тест и посмотреть, сможет ли он исправить косяки GPT (она делает косяки на всех вопросах кроме тривиальных и их комбинаций).

Также вариантом может быть делать coding интервью только в офисе, в комнате, отключенной от интернета, с полным обзором от интервьюера. Но после трех лет ковида это может быть трудно.

UPD: Также я заметил, что ChatGPT часто пишет в стиле, в котором писал бы программист, впервые увидевший верилог, а не проектировщик железа. Например использует initial для инициализации вместо сброса (что неверно по двум причинам: несинтезируемо для ASIC + multiple drivers). А также устаревший формат sensitivity list. То есть семантическую модель кодирования на верилоге им делал(и) программисты, которые воспринимают верилог как еще один язык программирования.

|

|

Серенада Трубадура в исполнении Юрия Панчула 2022-12-12 |

Для концерта студии Марии Беличенко исполнил серенаду Трубадура ("Луч солнца золотого" из мультфильма Возвращение Бременских Музыкантов.

https://mariaflute.com/

|

|

Как Америка любила и бодалась с Huawei — и как та ответила |

10 лет назад в Санта-Клара, Калифорния, неподалеку от Интела и NVidia, стоял кампус Huawei. В нем работали не только китайцы, но и вообще обычная публика Silicon Valley - индусы, американцы, даже русские попадались. Бизнесмены калифорнийских электронных компаний говорили "Huawei - это дверь в Китай" и заключали с ними крупные сделки.

Но американское правительство Huawei невзлюбило. Можно обсусоливать те или иные поводы, но коренная причина понятна - американскому правительству хочется, чтобы Америка сохраняла технологическое преимущество. Ибо если технология коммодифицируется и айфон не будет ничем особенным, то кто будет читать брошурки про продвижение демократии, распостраняемые американскими посольствами в других странах? Над ними будут просто смеяться.

И вот правительство начало Huawei жучить - и от Андроида отлучило, и от других критических технологий. Но на всяких хитрецов найдется гайка с левой резьбой. И вот что Huawei стал делать по этому поводу.

Но начнем по порядку. Вот как выглядел кампус Huawei на пересечении Central Expressway с San Tomas Expressway (Центральное Шоссе и Шоссе Святого Фомы Аквинского) в Санта-Кларе:

Я в эти здания заходил, так как работал с Huawei в совместном проекте от лица MIPS и даже получил за это табличку на стену:

Про сам проект прессе были известны только слухи, хотя с Huawei / HiSilicon работал не только MIPS, но и например IBM Microelectronics. Про IBM я узнал совершенно случайно, наткнувшись на инженера из этого проекта во время отпуска в Юте. Главное СМИ электронной промышленности, Electronic Engineering Times, писало про проект загадочно, в рубрике EE Times Confidential:

Потом настало это:

Но Huawei - не такая компания, чтобы покорно ползти в могилу из-за каких-то госдеповских бюрократов. Они бодро начали импортозамещение, в том числе в области программ для проектировщиков микросхем, и сразу наняли 50 молодых PhD на разработку алгоритмов EDA (Electronic Design Automation - автоматизация проектирования электроники, по русски САПР):

Я вспомнил про случай Huawei / HiSilicon, когда на днях мне прислал емейл Андрей Садовых из казанского Иннополиса и попросил придумать задачку для их хакатона по программам автоматизации проектирования CASE in Tools 2022.

Я уже участвовал в таком хакатоне как задачкодатель в 2020 году и описал задачку по трассировке и размещению логических элементов микросхемы на Хабре (пост до хакатона и после). Вот команда, которая решила мою задачку и получила приз:

Итак, новая задачка. Назовем ее "Подсчет количества D-триггеров в схеме на основе анализа кода на языке описания аппаратуры SystemVerilog (без учета оптимизации)".

Немного картины с высоты птичьего полета.

Разработчика блока микросхемы оценивают не только по отсутствию функциональных багов, но и по PPA - Power-Performance- Area или Энергопотребление-Производительность-Площадь. При этом:

- В энергопотреблении выделают статическое (все время) и динамическое (пропорционально переключениям, зависит от конкретного теста);

- Производительность разделяют на пропускную способность (сколько транзакций проходит через блок за N тактов) и тактовую частоту (1 / сколько длится такт);

- Площадь делят на размер блоков встроенной статической памяти и площадь под стандартные ячейки.

Для грубой оценки площади под стандартные ячейки в микросхемах ASIC удобно использовать количество D-триггеров, минимальных элементов состояния / памяти. Это связано с тем, что пропорция ячеек комбинационной логики к количеству D-триггеров во многих типах схем статистически сходна и именно количество D-триггеров является узким местом. В FPGA ситуация несколько другая - там D-триггеров по сравнению с комбинационной логикой много и их не нужно так сильно экономить как в ASIC-ах.

Количество D-триггеров важно еще и потому, что своими переключениями они жрут много электроэнергии.

Короче, на проектировщика блока архитекторы чипа как правило спускают:

- Функциональную/архитектурную спецификацию;

- Требования к пропускной способности;

- Бюджет тактовой частоты;

- Бюджет количества D-триггеров;

- Общий бюджет площади, включающей площадь блоков статической памяти;

- Пожелания понизить энергопотребление по сравнению с предыдущим блоком на столько-то процентов.

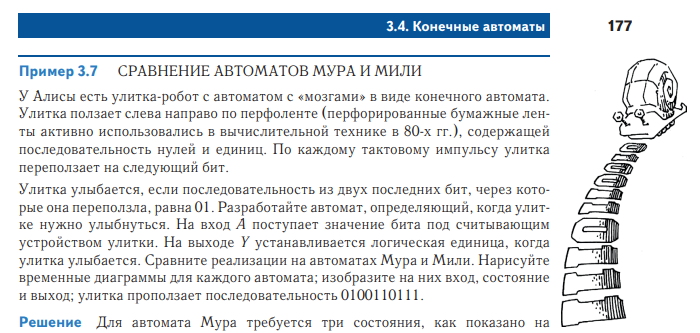

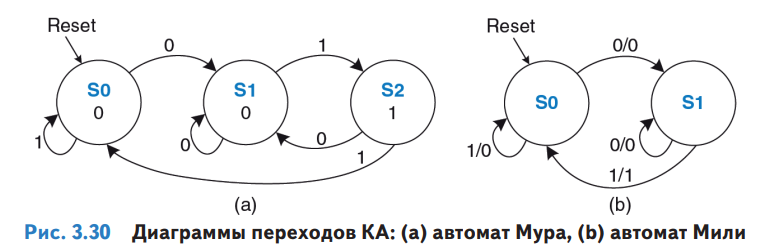

Суть задачи

Подсчитать количество комбинационных логических элементов в схеме, описанной на языке SystemVerilog - это однозначно не хакатонная задача - она требует сложной технологии логического синтеза. Но вот количество D-триггеров подсчитать гораздо проще - достаточно найти в коде все так называемые неблокирующие присваивания и суммировать размеры всех переменных, к которым они применяются.

Варианты задачи разной сложности

Разумеется, при этом возникает много трудностей. В зависимости от формулировки задачу подсчета D-триггеров на основе кода можно решить за любое время от 1 часа до 1 года. Перечислим эти трудности (потом мы перечислим их снова, но уже с картинками):

- Разработчик / писатель кода на верилоге мог по неаккуратности использовать блокирующие, а не неблокирующие присваивания. Мы не рассматриваем этот вариант - мы будем считать, что писатель кода жестко следовал рекомендуемой методологии проектирования.

- Для простейшего варианта хакатона (на час) можно написать простой скрипт на питоне, который будет работать только если все переменные явлются однобитными; для более интересного хакатона (на день) стоит рассматривать многобитовые вектора; для еще более интересного (на пару дней) - многомерные массивы, а для варианта на год - все структуры данных в языке SystemVerilog.

- Для целей хакатона вероятно стоит парсировать код, в котором не используются директивы препроцессора (`define), нет параметризации (parameter, localparam) и нет конструкции generate. Хотя если реализация на хакатоне делается на основе существующего open-source парсера верилога (например из Icarus Verilog или из Yosys), то можно попробывать обрабатывать код и со всеми этими конструкциями.

- Для простого хакатона наверное стоит подсчитывать D-триггеры только в одном модуле. Для более сложного стоит парсировать и модульную иерархию.

Инструментарий

Мне честно говоря самому интересно, до чего дойдут студенты. Как я уже сказал:

1) Простейший вариант (без иерархии, параметризации и с однобитовыми переменными) можно написать на языке типа питона или джавы за час.

2) Если использовать многобитовые переменные и многомерные массивы, на решение может уйти еще полдня, но того же питона тоже должно хватить. Возможно понадобиться применить регулярные выражения.

3) Модульная иерархия вносит дополнительные сложности. Помимо быстрого кодирования на питоне или джаве (на что может уйти день) стоит рассмотреть вариант освоить чужой парсер верилога на C++ (Icarus Verilog или Yosys) и модифицировать его для этой задачи.

Иллюстрации частных случаев

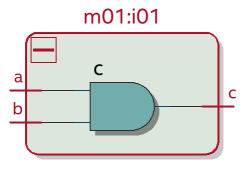

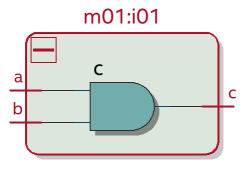

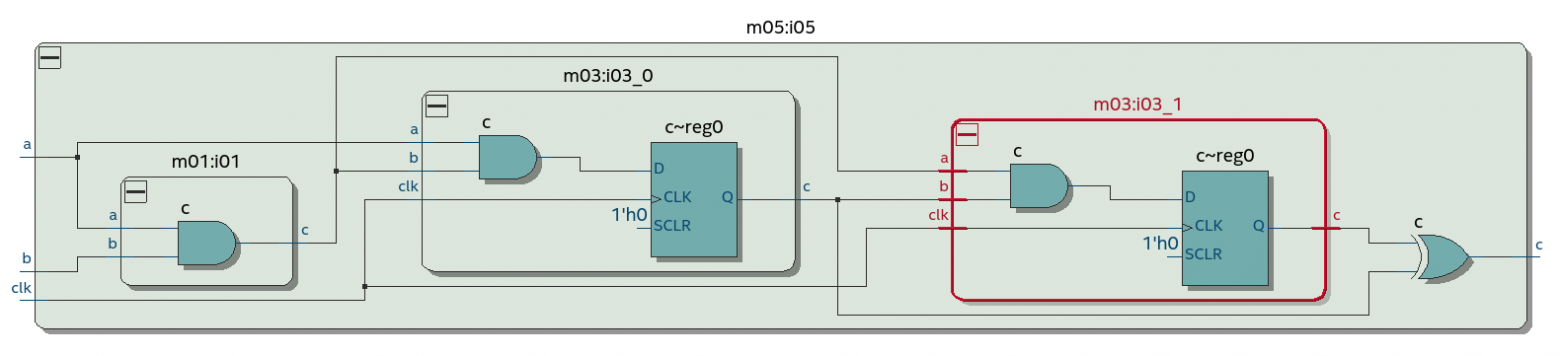

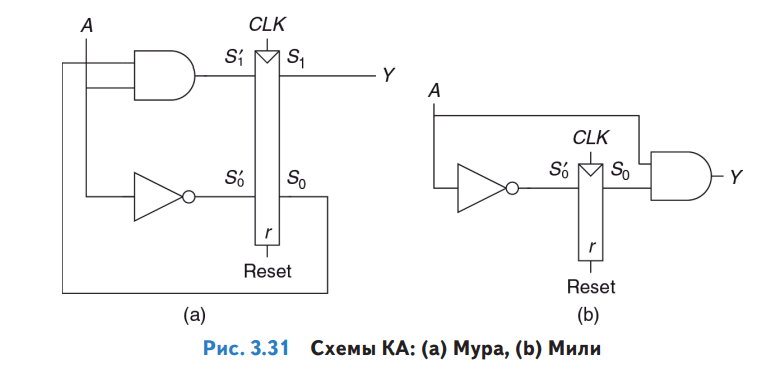

Теперь то же самое, но с картинками. Первые два модуля вообще не содержат никаких D-триггеров - в них нет ни always-блока по фронту, ни неблокирующих присваиваний ("<="). Только блокирующее внутри "always_comb" ("=") :

Такая схема синтезируется в двух-входовый логический элемент И:

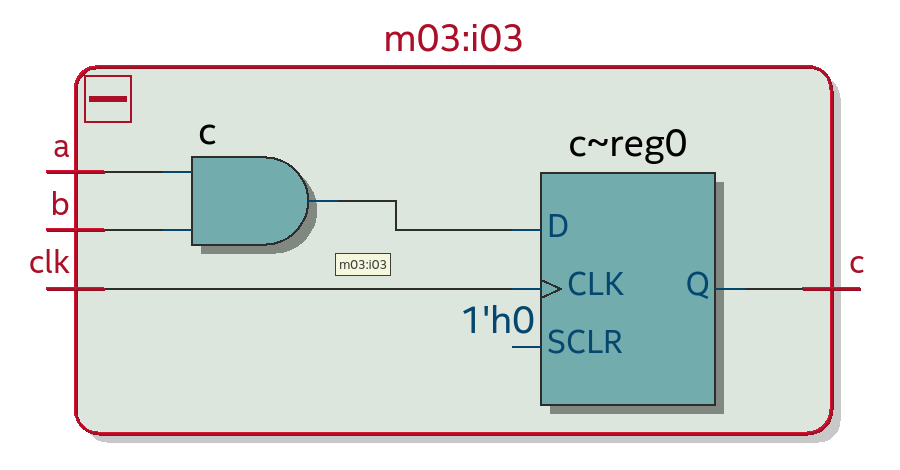

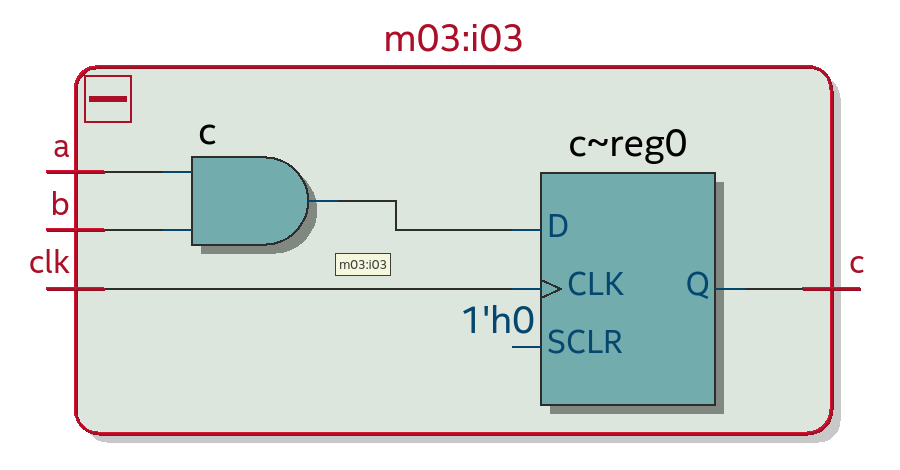

А вот как выглядит код, порождающий D-триггер. В нем есть неблокирующее присваивание ("<=") к переменной "c" которая объявлена как выходной порт и имеет размер 1 бит.

Неблокирующее присваивание находится внутри always-блока по фронту тактового сигнала (хакатонное решение может игнорировать этот факт, обращая внимание только на переменную, к которой применяется неблокирующее присваивание).

Также важно не спутать неблокирующее присваивание с операцией "меньше или равно" которая тоже пишется как "<=".

Этот код соответствует следующей схеме. Квадратик на ней - это D-триггер:

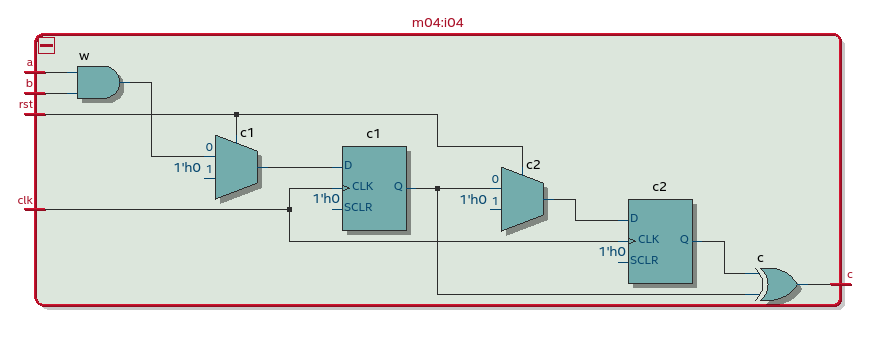

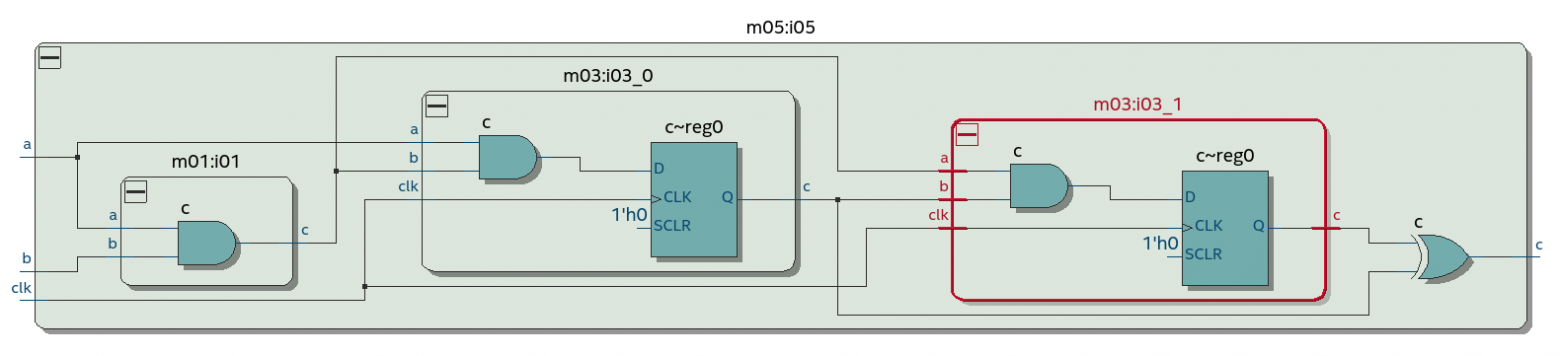

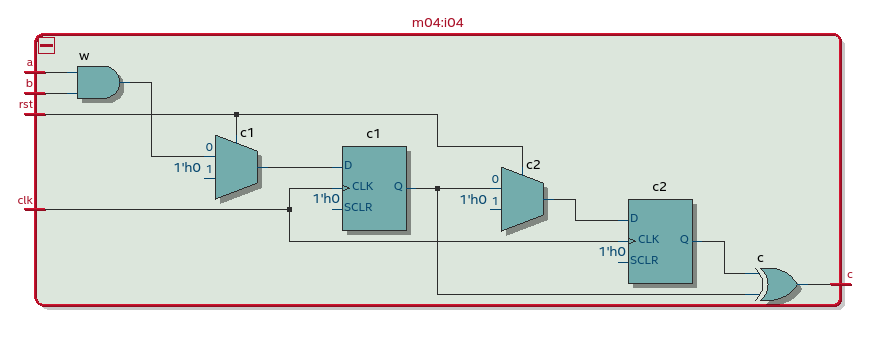

Несколько неблокирующих присваиваний к одной и той же переменной не порождают несколько D-триггеров. Но неблокирующие присваивания к разным переменным - порождают. В примере слева неблокирующие присваивания делаются двум однобитовым переменным, что порождает два D-триггера. Синхронные сбросы у этих D-триггеров перед оптимизацией превращаются в мультиплексоры, но это не важно для нашей цели подсчета D-триггеров:

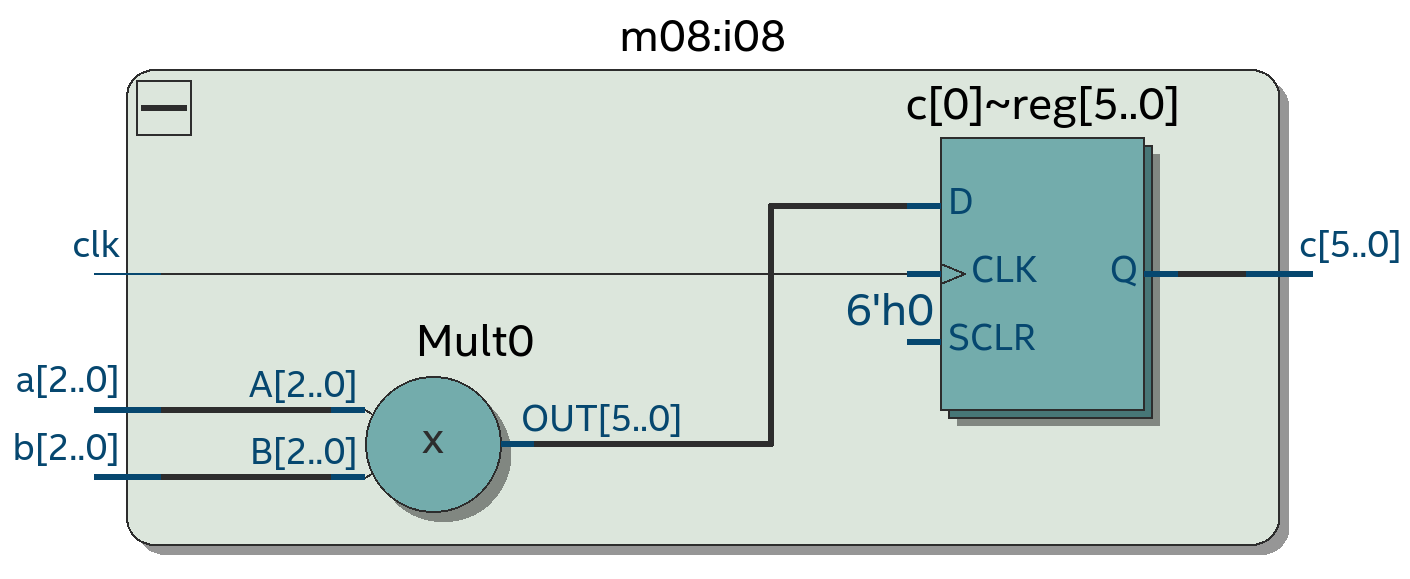

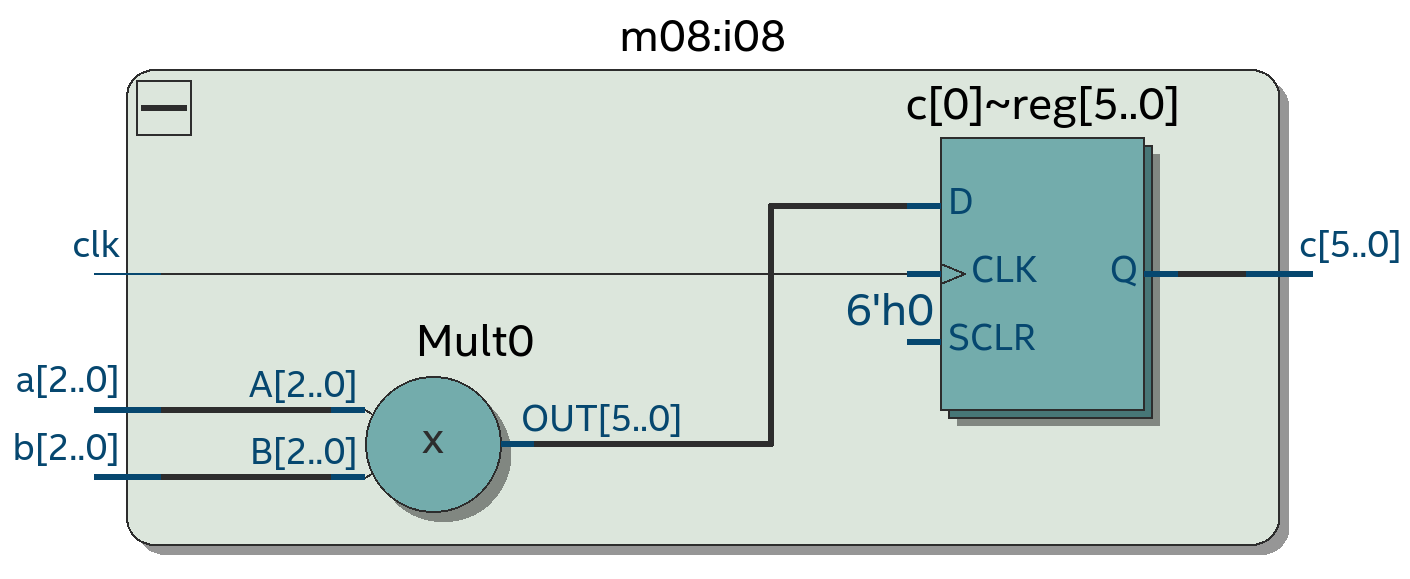

Следующее усложнение хакатона - это добавление переменных шириной в несколько бит. В примере ниже результат умножения двух 3-битных чисел "a" и "b" помещается в регистр "c" шириной 6 бит. Регистр - это просто группа из D-триггеров, которая в данном случае состоит из D-триггеров c[5], c[4], c [3], c [2], c[1] и c[0]:

Если усложнить задачу вне рамок хакатона, такой модуль можно параметризовать - либо с помощью препроцессора (слева), либо с помощью ключевого слова "parameter" справа:

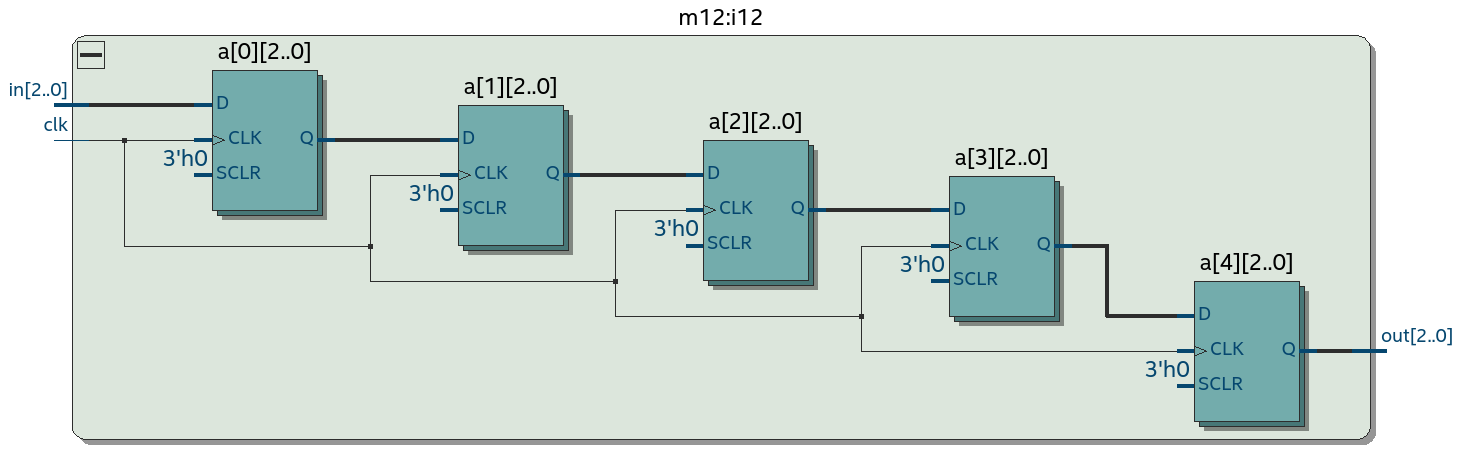

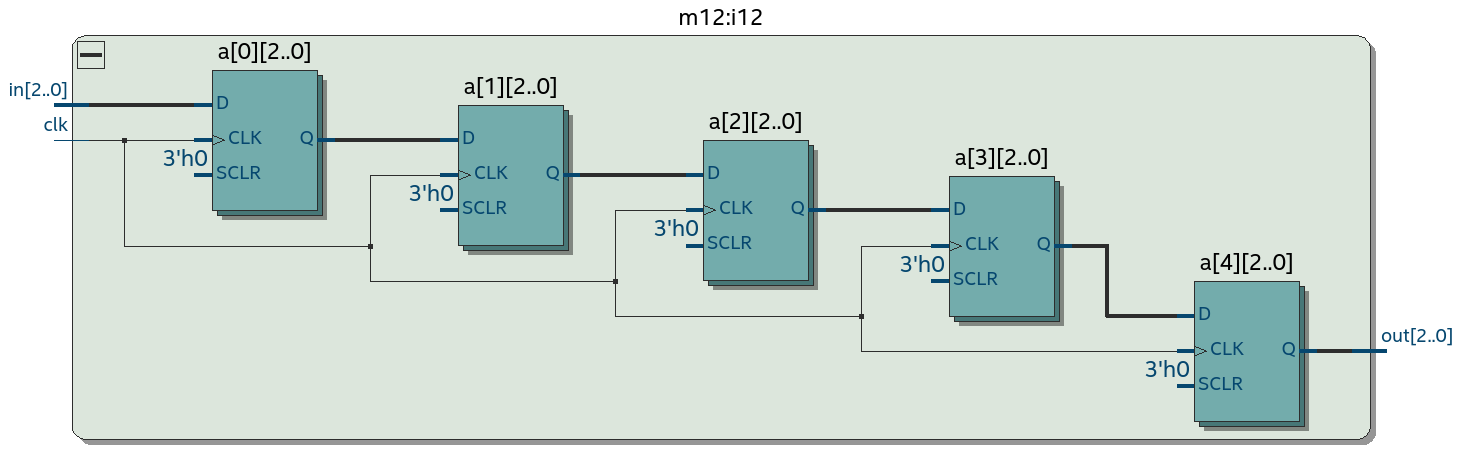

Другое важное усложнение, которое стоит сделать во время хакатона - это неупакованные массивы с размерностью справа от идентификатора. Слева пример схемы сдвигового регистра шириной 3 бита и глубиной 5 элементов, который использует 3 * 5 = 15 D-триггеров.

Вот как выглядит схема такого сдвигового регистра, обратите внимание что D-триггеры одного элемента собраны в "книжечки" по 3:

Стандарт SystemVerilog также поддерживает синтаксис "logic [2:0] a [5]" вместо "logic [2:0] a [0:4]". Вне рамок хакатона можно было бы написать программу, которая подсчитывает D-триггеры для сложных типов данных, например структур:

Наконец, было бы хорошо (возможно не на хакатоне, а после него) написать программу, которая бы парсировала иерархию модулей и подсчитывала D-триггеры на всех уровнях. Модули в верилоге как матрешки, за исключением того, что одной и той же матрешки может быть несколько экземпляров - D-триггеры во всех экземплярах нужно суммировать, это не как в софтвере с вызовами функций;

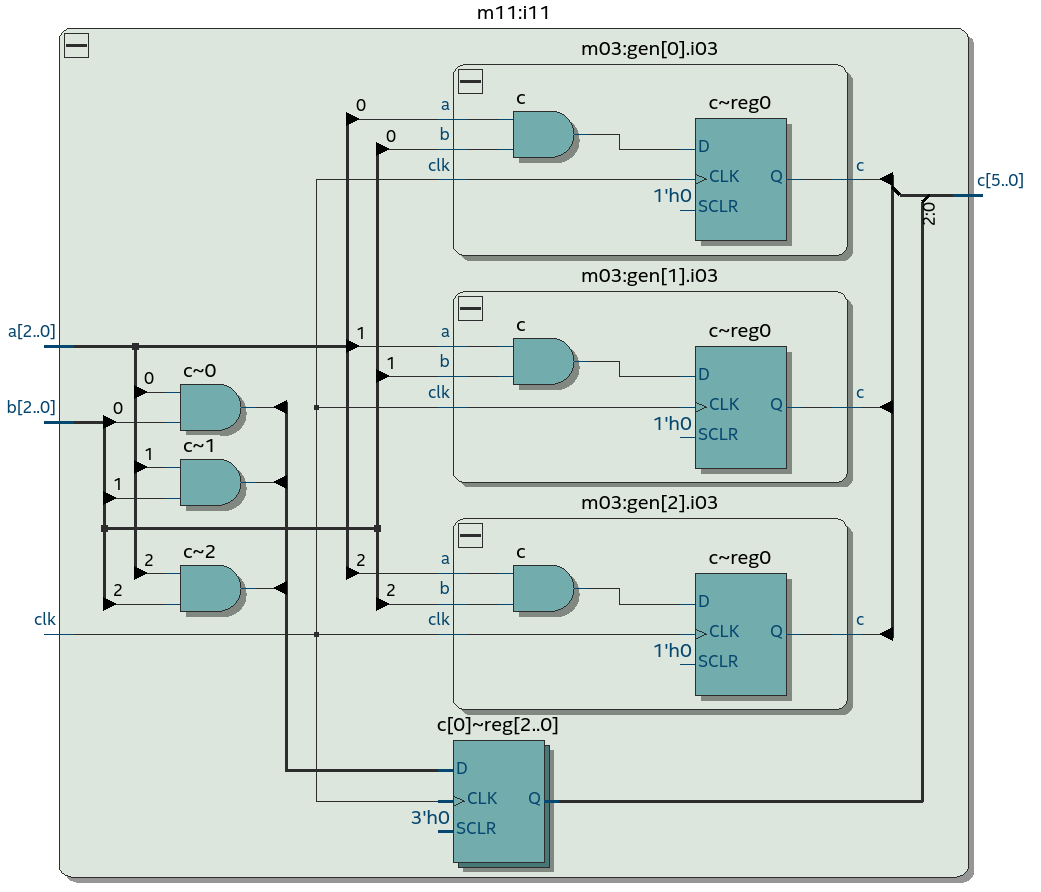

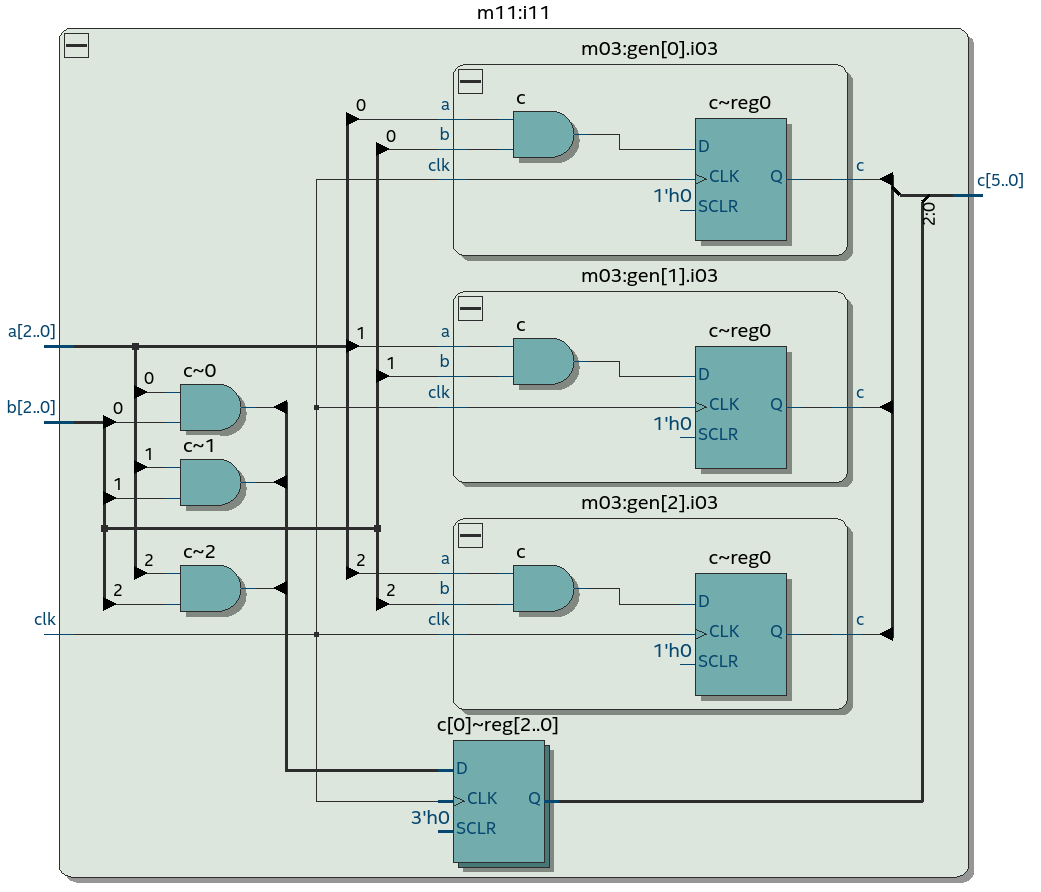

А вот случай использования конструкции generate. Его имхо можно покрыть на хакатоне только если использовать чей-то готовый open-source парсер:

То что выглядит синтаксически как софтверный цикл - на самом деле не цикл, а своего рода макро, порождающее несколько экземпляров модуля m03 (D-триггеры в них нужно суммировать).

В этой схеме при w=3 будет шесть D-триггеров - три из always-блока на верхнем уровне и три из трех экземпляров модуля второго уровня m03.

Я надеюсь, что какая-нибудь команда в Иннополисе не напугается и примет мою задачу. Она, при разумной формулировке, проще, чем может показаться из моей заметки. В худшем случае можно сделать "grep '<=' | sed ... | sort -u | wc -l" - и объявить задачу выполненной (это вполне ответ для формулировки задачи без иерархии и с однобитовыми переменными).

Так что успехов и вперед. Это поможет вам нарастить скиллы в компиляторах, скриптинге и разумеется основах цифрового проектирования - очень ценный рабочий навык в современной международной обстановке.

Задание уже выложено на сайт

Вот описание на английском:

Electronic Design Automation (EDA)

Yuri Panchul is an electronic chip designer (MIPS, Juniper and other companies); a founder of an EDA startup C Level Design acquired by Synopsys, an editor of a book published by HSE MIEM and an author of an online course developed by RUSNANO.

Context: When a chip architect gives a hardware block designer the architectural specification for a new block, he also gives the designer a set of requirements. These requirements include:

1. The performance or bandwidth: a number of instructions, transactions, network packets or graphical primitives processed by the block in a number of clock cycles.

2. The timing budget: the number of picoseconds available for the combinational logic to stabilize within one clock period. In order words, the required clock frequency.

3. The total area budget, which includes the area for the embedded SRAMs and the ASIC standard cells.

In addition, the designer gets guidance on power optimization. One of the key metrics related to both area and power is the count of D-flip-flops (DFFs), the main state elements in digital design. DFFs are used to build hardware pipelines, state machines, FIFO queues and CPU scoreboards. The designer:

1. Receives the DFF budget from the chip architect;

2. Estimates the number of DFFs required for each sub-block early in the design cycle; and

3. Tracks this number every week till the chip tapeout.

A digital design is almost always done using a hardware description language: Verilog, SystemVerilog or VHDL. The technology that converts a Verilog code into a graph of logic elements is called logic synthesis. The synthesis technology is complicated and not suitable for a hackathon. However it is possible to approximately count the number of DFFs even without full synthesis, just by finding so-called non-blocking assignments in Verilog code and adding the sizes of the variables on the left-hand sides of non-blocking assignments.

Task: Write a program that estimates the number of D-flip-flops in an electronic circuit by a quick analysis of its Verilog source code.

Instruments: this problem has multiple levels of difficulty, depending on how much Verilog syntax we are willing to support:

1. If we restrict the input code to single-bit variables within a single module, we can write just a few Linux commands that do the job. We can grep for '<=' non-blocking assignment characters, then collect the unique identifiers on the left-hand sides of non-blocking assignments and report their number. An experienced Linux user can write a simple "grep|sed|sort|wc" pipeline for it in a few minutes.

2. A more complicated case, with parsing bit vectors and unpacked arrays, would take longer, up to several hours. You can use regular expressions in Python or Lex & Yacc - style parsers in C or Java.

3. If we are going to support counting DFFs in the Verilog module hierarchy, we need to parse module instantiations and build the instance tree. This adds hours of programming but can still be done during a short hackathon.

4. If we extend the task to support Verilog preprocessor, parameterized modules, "generate" constructs, "struct" types and the assignments inside Verilog "tasks", we probably need a "real" Verilog parser. There are some open-source parsers of Verilog, including Yosys, Icarus Verilog and Verilator. Your hackathon team can study and utilize them if you wish to go this way.

Whatever you decide to do you are likely to get a good experience in scripting, compilers and digital design.

For more details see the description of the project in an article on the Habr website (in Russian) https://habr.com/ru/post/702186/

|

|

Как Америка любила и бодалась с Huawei |

10 лет назад в Санта-Клара, Калифорния, неподалеку от Интела и NVidia, стоял кампус Huawei. В нем работали не только китайцы, но и вообще обычная публика Silicon Valley - индусы, американцы, даже русские попадались. Бизнесмены калифорнийских электронных компаний говорили "Huawei - это дверь в Китай" и заключали с ними крупные сделки.

Но американское правительство Huawei невзлюбило. Можно обсусоливать те или иные поводы, но коренная причина понятна - американскому правительству хочется, чтобы Америка сохраняла технологическое преимущество. Ибо если технология коммодифицируется и айфон не будет ничем особенным, то кто будет читать брошурки про продвижение демократии, распостраняемые американскими посольствами в других странах? Над ними будут просто смеяться.

И вот правительство начало Huawei жучить - и от Андроида отлучило, и от других критических технологий. Но на всяких хитрецов найдется гайка с левой резьбой. И вот что Huawei стал делать по этому поводу.

Но начнем по порядку. Вот как выглядел кампус Huawei на пересечении Central Expressway с San Tomas Expressway (Центральное Шоссе и Шоссе Святого Фомы Аквинского) в Санта-Кларе:

Я в эти здания заходил, так как работал с Huawei в совместном проекте от лица MIPS и даже получил за это табличку на стену:

Про сам проект прессе были известны только слухи, хотя с Huawei / HiSilicon работал не только MIPS, но и например IBM Microelectronics. Про IBM я узнал совершенно случайно, наткнувшись на инженера из этого проекта во время отпуска в Юте. Главное СМИ электронной промышленности, Electronic Engineering Times, писало про проект загадочно, в рубрике EE Times Confidential:

Потом настало это:

Но Huawei - не такая компания, чтобы покорно ползти в могилу из-за каких-то госдеповских бюрократов. Они бодро начали импортозамещение, в том числе в области программ для проектировщиков микросхем, и сразу наняли 50 молодых PhD на разработку алгоритмов EDA (Electronic Design Automation - автоматизация проектирования электроники, по русски САПР):

Я вспомнил про случай Huawei / HiSilicon, когда на днях мне прислал емейл Андрей Садовых из казанского Иннополиса и попросил придумать задачку для их хакатона по программам автоматизации проектирования CASE in Tools 2022.

Я уже участвовал в таком хакатоне как задачкодатель в 2020 году и описал задачку по трассировке и размещению логических элементов микросхемы на Хабре (пост до хакатона и после). Вот команда, которая решила мою задачку и получила приз:

Итак, новая задачка. Назовем ее "Подсчет количества D-триггеров в схеме на основе анализа кода на языке описания аппаратуры SystemVerilog (без учета оптимизации)".

Немного картины с высоты птичьего полета.

Разработчика блока микросхемы оценивают не только по отсутствию функциональных багов, но и по PPA - Power-Performance- Area или Энергопотребление-Производительность-Площадь. При этом:

- В энергопотреблении выделают статическое (все время) и динамическое (пропорционально переключениям, зависит от конкретного теста);

- Производительность разделяют на пропускную способность (сколько транзакций проходит через блок за N тактов) и тактовую частоту (1 / сколько длится такт);

- Площадь делят на размер блоков встроенной статической памяти и площадь под стандартные ячейки.

Для грубой оценки площади под стандартные ячейки в микросхемах ASIC удобно использовать количество D-триггеров, минимальных элементов состояния / памяти. Это связано с тем, что пропорция ячеек комбинационной логики к количеству D-триггеров во многих типах схем статистически сходна и именно количество D-триггеров является узким местом. В FPGA ситуация несколько другая - там D-триггеров по сравнению с комбинационной логикой много и их не нужно так сильно экономить как в ASIC-ах.

Количество D-триггеров важно еще и потому, что своими переключениями они жрут много электроэнергии.

Короче, на проектировщика блока архитекторы чипа как правило спускают:

- Функциональную/архитектурную спецификацию;

- Требования к пропускной способности;

- Бюджет тактовой частоты;

- Бюджет количества D-триггеров;

- Общий бюджет площади, включающей площадь блоков статической памяти;

- Пожелания понизить энергопотребление по сравнению с предыдущим блоком на столько-то процентов.

Суть задачи

Подсчитать количество комбинационных логических элементов в схеме, описанной на языке SystemVerilog - это однозначно не хакатонная задача - она требует сложной технологии логического синтеза. Но вот количество D-триггеров подсчитать гораздо проще - достаточно найти в коде все так называемые неблокирующие присваивания и суммировать размеры всех переменных, к которым они применяются.

Варианты задачи разной сложности

Разумеется, при этом возникает много трудностей. В зависимости от формулировки задачу подсчета D-триггеров на основе кода можно решить за любое время от 1 часа до 1 года. Перечислим эти трудности (потом мы перечислим их снова, но уже с картинками):

- Разработчик / писатель кода на верилоге мог по неаккуратности использовать блокирующие, а не неблокирующие присваивания. Мы не рассматриваем этот вариант - мы будем считать, что писатель кода жестко следовал рекомендуемой методологии проектирования.

- Для простейшего варианта хакатона (на час) можно написать простой скрипт на питоне, который будет работать только если все переменные явлются однобитными; для более интересного хакатона (на день) стоит рассматривать многобитовые вектора; для еще более интересного (на пару дней) - многомерные массивы, а для варианта на год - все структуры данных в языке SystemVerilog.

- Для целей хакатона вероятно стоит парсировать код, в котором не используются директивы препроцессора (`define), нет параметризации (parameter, localparam) и нет конструкции generate. Хотя если реализация на хакатоне делается на основе существующего open-source парсера верилога (например из Icarus Verilog или из Yosys), то можно попробывать обрабатывать код и со всеми этими конструкциями.

- Для простого хакатона наверное стоит подсчитывать D-триггеры только в одном модуле. Для более сложного стоит парсировать и модульную иерархию.

Инструментарий

Мне честно говоря самому интересно, до чего дойдут студенты. Как я уже сказал:

1) Простейший вариант (без иерархии, параметризации и с однобитовыми переменными) можно написать на языке типа питона или джавы за час.

2) Если использовать многобитовые переменные и многомерные массивы, на решение может уйти еще полдня, но того же питона тоже должно хватить. Возможно понадобиться применить регулярные выражения.

3) Модульная иерархия вносит дополнительные сложности. Помимо быстрого кодирования на питоне или джаве (на что может уйти день) стоит рассмотреть вариант освоить чужой парсер верилога на C++ (Icarus Verilog или Yosys) и модифицировать его для этой задачи.

Иллюстрации частных случаев

Теперь то же самое, но с картинками. Первые два модуля вообще не содержат никаких D-триггеров - в них нет ни always-блока по фронту, ни неблокирующих присваиваний ("<="). Только блокирующее внутри "always_comb" ("=") :

Такая схема синтезируется в двух-входовый логический элемент И:

А вот как выглядит код, порождающий D-триггер. В нем есть неблокирующее присваивание ("<=") к переменной "c" которая объявлена как выходной порт и имеет размер 1 бит.

Неблокирующее присваивание находится внутри always-блока по фронту тактового сигнала (хакатонное решение может игнорировать этот факт, обращая внимание только на переменную, к которой применяется неблокирующее присваивание).

Также важно не спутать неблокирующее присваивание с операцией "меньше или равно" которая тоже пишется как "<=".

Этот код соответствует следующей схеме. Квадратик на ней - это D-триггер:

Несколько неблокирующих присваиваний к одной и той же переменной не порождают несколько D-триггеров. Но неблокирующие присваивания к разным переменным - порождают. В примере слева неблокирующие присваивания делаются двум однобитовым переменным, что порождает два D-триггера. Синхронные сбросы у этих D-триггеров перед оптимизацией превращаются в мультиплексоры, но это не важно для нашей цели подсчета D-триггеров:

Следующее усложнение хакатона - это добавление переменных шириной в несколько бит. В примере ниже результат умножения двух 3-битных чисел "a" и "b" помещается в регистр "c" шириной 6 бит. Регистр - это просто группа из D-триггеров, которая в данном случае состоит из D-триггеров c[5], c[4], c [3], c [2], c[1] и c[0]:

Если усложнить задачу вне рамок хакатона, такой модуль можно параметризовать - либо с помощью препроцессора (слева), либо с помощью ключевого слова "parameter" справа:

Другое важное усложнение, которое стоит сделать во время хакатона - это неупакованные массивы с размерностью справа от идентификатора. Слева пример схемы сдвигового регистра шириной 3 бита и глубиной 5 элементов, который использует 3 * 5 = 15 D-триггеров.

Вот как выглядит схема такого сдвигового регистра, обратите внимание что D-триггеры одного элемента собраны в "книжечки" по 3:

Стандарт SystemVerilog также поддерживает синтаксис "logic [2:0] a [5]" вместо "logic [2:0] a [0:4]". Вне рамок хакатона можно было бы написать программу, которая подсчитывает D-триггеры для сложных типов данных, например структур:

Наконец, было бы хорошо (возможно не на хакатоне, а после него) написать программу, которая бы парсировала иерархию модулей и подсчитывала D-триггеры на всех уровнях. Модули в верилоге как матрешки, за исключением того, что одной и той же матрешки может быть несколько экземпляров - D-триггеры во всех экземплярах нужно суммировать, это не как в софтвере с вызовами функций;

А вот случай использования конструкции generate. Его имхо можно покрыть на хакатоне только если использовать чей-то готовый open-source парсер:

То что выглядит синтаксически как софтверный цикл - на самом деле не цикл, а своего рода макро, порождающее несколько экземпляров модуля m03 (D-триггеры в них нужно суммировать).

В этой схеме при w=3 будет шесть D-триггеров - три из always-блока на верхнем уровне и три из трех экземпляров модуля второго уровня m03.

Я надеюсь, что какая-нибудь команда в Иннополисе не напугается и примет мою задачу. Она, при разумной формулировке, проще, чем может показаться из моей заметки. В худшем случае можно сделать "grep '<=' | sed ... | sort -u | wc -l" - и объявить задачу выполненной (это вполне ответ для формулировки задачи без иерархии и с однобитовыми переменными).

Так что успехов и вперед. Это поможет вам нарастить скиллы в компиляторах, скриптинге и разумеется основах цифрового проектирования - очень ценный рабочий навык в современной международной обстановке.

|

|

Миротворец: как я на нем оказался — и другой дискурс русскоязычного украинского американца |

Записал с Ruslan Gurzhiy из "Славянского Сакраменто" видео своего обычного дискурса на 1 час 20 минут.

Обычная тема: главный источник бед Украины заключается в том, что:

1. Сначала люди воспринимают "Запад" как одно целое, вместо разделения его на части: политизированной группы в Госдепе и коммерческих компаний.

2. Потом они вместо того чтобы работать с коммерческими компанями над экономическим и технологическим развитием, слушаются Госдепа и всяких активистов.

3. Госдеп Украину развить не может, так как условный Макфол не может научить украинцев делать айфоны, а также не может приказать компаниям Silicon Valley приехать на Украину что-то там направить и обустроить.

4. Украинские активисты-националисты в технологическом и экономическом развитии ничего не понимают, а замкнуты в цикле магического мышления, что если бить себя в грудь "мы не русские", то прилетит с Запада волшебник на голубом вертолете, всех выстроит в шеренгу, даст европейские зарплаты и скажет как идти. "Мы к этому готовы" типа "в ожидании этого на украинский язык переходим".

5. На самом деле европейским и американским компаниям вообще наплевать, на каком языке говорят на Украине. Именно с ними нужно было работать проактивно, как это делали например российкие электронные компании последние 10 лет - сами лицензировали всякие процессорные ядра и заключали контракты. Также в России развели курсы по обучению студентов FPGA и ASIC design, на которые российские студенты сейчас активно ходят и которые приведут к реальному развитию, когда вся ситуация как-то утрясется через какое-то время. Совершенно независимо от того, чей будет Крым и Донбасс.

Короче, кто работает, учится и проактивен - то и прав. Кто ожидает у моря золотую рыбку и пытается только требовать у заокеанских господ прижучить тех, кто работает - то остается у разбитого корыта.

Пояснение к слову "работа": "работа" означает вначале решать всякие задачки по верилогу, потом делать open-source проекты, а потом коммерческие маркетируемые проекты. А не "работа" в смысле "мы работает с комитетом Slush, чтобы они отняли миллион у русских победителей конкурса". Это не работа, а фигня, победителем таким образом стать нельзя.

Больше такого - в видео

|

|

Обнаружил баг американской системы образования |

Обнаружил интересный баг американской системы образования:

У многих студентов в резюме стоит "делал курсовой проект по алгоритму Томасуло, out-of-order суперскаляру, многопоточному процессору итд".

На это я спрашиваю: "Прекрасно, давайте возьмем два процессорных ядра - одно со статическим конвейером, а у другого с динамическим, как в вашем курсовике. Насколько ваш процессор будет производительнее?"

На это они отвечают "процессор будет производительнее, потому что" - и начинают ковыряться в деталях зависимостей между инструкциями.

На это я машу руками и говорю "стоп-стоп-стоп. Я не просил вас объяснить мне что такое RaW (read-after-write), WaR и WaW зависимости. Я вообще не спрашивал у вас "почему?" Я спросил у вас "сколько?" Я просил вас грубо оценить пользу от вашей разработки.

Вот вы вместе с другими студентами, под руководством профессора проектировали процессор, делали довольно сложную, продвинутую оптимизацию. Теперь возьмем написанный вами верилог, запустим его в симуляторе и пропустим через него бенчмарку, скажем Dhrystone или CoreMark. Допустим у процессора со статическим конвейером сколько-то итераций бенчмарки прошли за сто тысяч тактов. За сколько тактов пройдет эта же бенчмарка на вашем процессоре - за сто тактов или за миллион? Или за что-то посередине? Сколько вы покупаете вашей оптимизацией - 1%, 10%, 100%? Какой ценой в размере логики? Может такты изменятся мало, но повысится максимальная тактовая частота? На сколько?"

И представляете, что они мне отвечают? "Мы не запускали бенчмарки".

Бенчмарки у них в учебниках есть - это я не думаю, а знаю, так как все их учебники стоят у меня на полке. Это выглядит для меня чисто как плохая работа преподавателей: преподаватели должны:

- Давать обзорную картину с высоты птичьего полета сколько покупают различные оптимизации и какой ценой.

- Подкреплять это знание измерением бенчмарков и статического анализа тайминга во время курсовых проектов. Также - если у университета есть доступ к Synopsys PTPX или Cadence Joules, то измерять динамическое энергопотребление. Но если нет - мерять такты и STA можно бесплатными тулами - Icarus Verilog и Open Lane.

Впрочем, в России и Украине проблем больше, чем у американских вузов: мне говорили несколько лет назад, что в МФТИ вообще обучали конвейерным процессорам с помощью cycle-accurate модели на C++, при этом без измерения статического анализа тайминга для разных вариантов микроархитектуры. Ну это как учить электричеству без магнетизма. Хотя с тех пор прошло время, и я надеюсь, что они это исправили.

|

|

По поводу выборов |

Помимо выборов в конгресс и сенат, мне как калифорнийскому избирателю, предложили проголосовать за следущее:

Prop 1. Поправка к конституции Калифорнии, гарантирующая аборты и презервативы.

Как человек с биологическим образованием (я получил associate degree по биологии в Foothill College) я рассматриваю аборт как несомненное убийство. Оплодотворенная яйцеклетка - уже диплоидный Homo sapiens, просто на ранней стадии своего развития.

Но я не против того, чтобы те или иные люди сами своими руками убирали свой геном из популяции. Это их личное дело, пусть убивают.

Насчет презервативов - я за только при условии, если государство поощрит налоговыми льготами производителей lambskin condoms (презервативов из кишки ягнят) - с ними секс для мужчины интереснее (женщинам вроде все равно - lambskin или latex).

Prop 26. Разрешать ли индейским племенам делат спортивные ставки а-ля ипподром в дополнение к азартным играм в своих резервациях.

и Prop 27. Разрешать такое же вне резервации, если это крышуется индейским племенем.

Я против. Пусть играют в трехмерные шутеры на телефонах - от этого мне идет зарплата.

Prop 28. Увеличить траты в школа на обучение искусству.

Я за. Работа в области искусства меня влекла к себе давно.

Prop 29. Увеличить количество левых ставок и бюрократии в больницах по диализу почек.

Против. Фельдшера или медсестры для базовых процедур должно быть достаточно. Или я не прав, что скажут медики и люди с больными почками?

Prop 30. Налоговые льготы для покупателей электрических автомобилей.

Мне электрический автомобиль не нужен. Я собираюсь на старости полгода в году жить в Москве, где буду ездить на метро и Яндекс-такси, а другие полгода в Калифорнии, где ходить пешком и ездить на трамвае VTA, иногда на юбере. Я вообще не фанат автомобилевождения. Кроме этого, электрические автомобили вреднее для природы чем бензиновые из-за производства литиевых аккумуляторов. Так что против.

Prop 31. Запрет на продажу ароматизированного табака.

Я бросил курить больше 20 лет назад, когда обнаружил, что страховые компании берут с курильщиков двое больше чем с некурящих. Так как страхование жизни - очень конкурентный бизнес, за этим должен стоять очень трезвый статистический анализ. Наверное стоит запретить.

При этом я на выборы не пошел. Я посмотрел на предварительные результаты и понял, что 1) с выборами в конгресс и сенат мой голос ничего не решает и 2) избиратели уже проголосовали за поправки как проголосовал бы я.

|

|

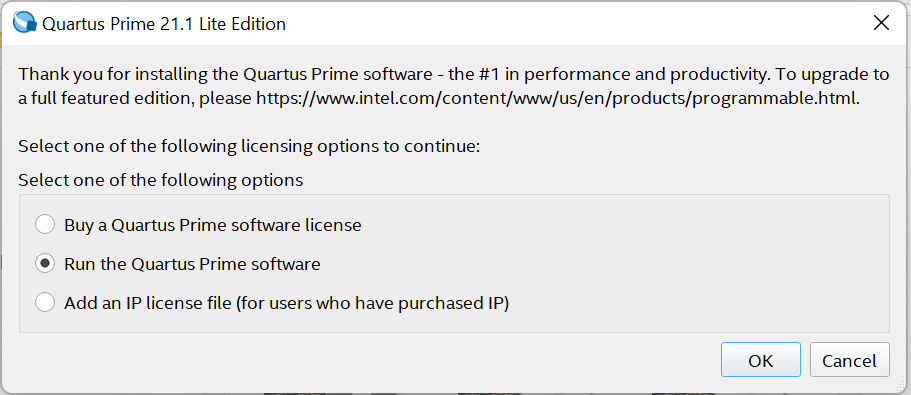

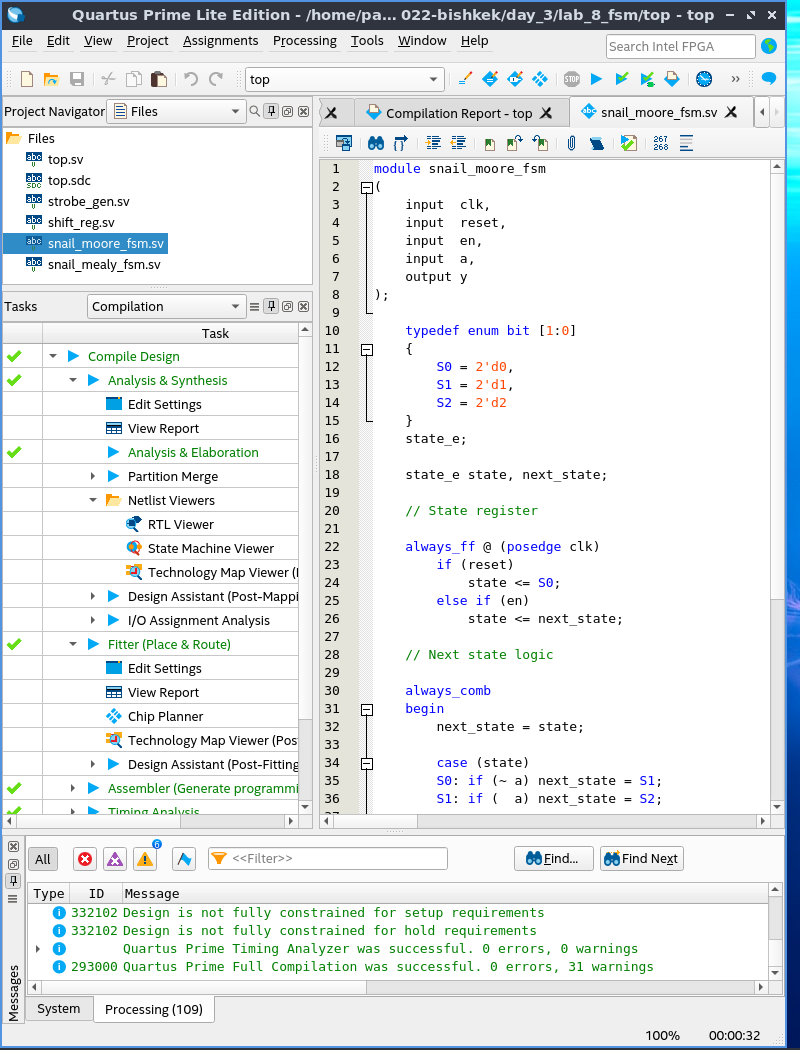

Как подготовиться к собеседованию в Samsung Advanced Computing Lab |

Я работаю проектировщиком аппаратного блока графического процессора в телефонах Samsung, в рамках совместного проекта с AMD. Сейчас наш менеджмент расширяет команду и поощряет инженеров распостранять информацию о новых позициях среди своих знакомых. Я решил написать это пост для более широкой аудитории, так как множество людей, способных пройти интервью на RTL или DV позицию - больше, чем множество моих знакомых. Если вы сможете прислать мне ответ на задачку в моем посте вместе с вашим резюме, я перешлю его нанимающему менеджеру и рекрутеру нашей группы (в комментах прошу ответ не писать). Если резюме им понравится, вам нужно будет пройти стандартное собеседование на несколько часов, с несколькими инженерами, у каждого из которых свой набор задачек.

Также я покажу материалы, по которым можно готовиться к собеседованию, особенно если вы студент или у вас ограниченный опыт в электронной промышлености.

Скажу сразу что для данных позиций нужно разрешение на работу в США. Если у вас его нет, я агитировать компанию за петицию на H-1 визу для вас не могу, но вы можете решить задачку чисто для расширения кругозора или демонстрации молодецкой удали.

Для опытных инженеров задачка слишком простая, но для недавних выпускников вузов по специальности Electrical Engineering или Computer Engineering - в самый раз. Это должен уметь решать выпускник практически любого американского вуза который брал курс типа MIT 6.111 Introductory Digital Systems Laboratory, а также выпускники российких вузов МИЭТ, МИРЭА, ВШЭ МИЭМ, ИТМО, Иннополис, МГУ ..., украинских КПИ, черниговского политеха, топ технических вузов Беларуси, Армении, Киргизии итд.

Ожидается, что вы владеете основами проектирования цифровых схем на уровне регистровых передач (Register Transfer Level - RTL), используя синтез с языка описания аппаратуры Verilog/SystemVerilog. Если вы напишете решение на VHDL - это тоже пойдет. Вы также можете приколоться и написать решение, используя high-level synthesis, графическую схему (schematic entry) или экзотические языки типа BlueSpec или Chisel, можете даже собрать ответ на советских микросхемах К155, транзисторах, радиолампах, реле или гидравлике - но все это я менеджменту не перешлю, хотя мне будет на это интересно посмотреть.

Итак, формулировка задачки:

Вам нужно спроектировать блок, который превращает поток данных шириной w бит в поток данных шириной w*2. Как прием узких данных в блок, так и передача широких данных из блока должна делаться с помощью valid/ready интерфейса в духе протокола AMBA AXI-Stream или каналов AXI4:

Вам также нужно написать тестовое окружение к блоку, которое обосновывает функциональную корректность и демонстрирует оптимальную пропускную способность блока. Большим плюсом будет, если вы еще и напишете код для проверки функционального покрытия, а также утверждения темпоральной логики, которые можно было бы проверить с помощью формальной верификации.

Valid/ready протокол должен следовать правилам, описанным для AXI (это все не ARM-specific и не AXI-specific, просто в армовской документации эти правила сформулированы лучше всего), в частности Valid не должен ждать Ready=1 для перехода от Valid=0 к Valid=1. Ведущий блок должен выставить Valid=1 не глядя на Ready, и потом ждать момента когда и Valid=1, и Ready=1 на положительном фронте тактового сигнала:

Ready может быть выставлен как через несколько тактов перед Valid, так и после Valid, или в том же такте что и Valid. Протокол Valid/Ready должен работать даже если Ready меняется случайно (в нашей задачке случайным может быть Downstream Ready для широкой шины). Также для оптимальной пропускной способности полезно обратить внимание на вот такое замечание в спецификации AXI (читать всю спецификацию не обязательно, я уже привел все что нужно для решения в этом после):

В отсутствие backpressure (то бишь когда downstream_rdy всегда равен 1), блок должен позволять прием данных каждый такт и выдачу данных через такт:

Полезная литература для подготовки к интервью

Вот самый лучший учебник начального уровня по вопросу, доступный сейчас на русском языке. Если вы не понимаете все, что в нем написано, то ваши шансы на трудоустройство в микроэлектронную компанию на RTL или DV (Design Verification) позицию не очень:

Вы также можете можете использовать более старый вариант учебника ниже. Главы 1-5 у учебников совпадают, но в главах 6-7 белый учебник использует модную молодежную архитектуру RISC-V, а зеленый - олдовую архитектуру MIPS. С точки зрения интервью на джуниор позицию RTL или DV инженера для проектирования или верификации GPU - это все равно.

Даже если вы будете проектировать не блок в подсистеме геометрии (как я) и не блок в pixel pipe, а шейдеры или управляющее ядро - даже в этом случае совершенно все равно, вы учились на MIPS или на RISC-V. Хотя с другой стороны, если вы учились (допустим) на микрокалькуляторе МК-54 или (допустим) на компьютерах ДВК и Радио-86, то вам нужно подучить концепцию конвейера (глава 7 и одного и другого учебника) для того, чтобы утверждать, что вы разбираетесь в основах архитектуры и микроархитектуры ЭВМ:

Подспорьем к учебнику Харрисов является вот такая книжка, которая привязывает его к упражнениям на платах с микросхемами регонфигурируемой логики ПЛИС / FPGA:

Но на одном учебнике Харрисов интервью вы не пройдете, так как в нем нет ряда тем, которые регулярно спрашивают на интервью, в частности задачки с очередями FIFO, арбитры, пересечение тактового домена, многопортовые памяти итд. Некоторые из тем, не разобранных у Харрисов, можно найти вот в такой книжке, по которой учатся в Стенфорде.

Например в ней есть про двойные буфера (skid buffers), асинхронные очереди FIFO для пересечения тактового домена (Clock Domain Crossing - CDC), работу с числами с плавающей точкой, немножко про банки памяти итд.

Но учебников недостаточно - стоит еще и читать всякие тексты из интернета, в частности статьи Клифа Каммингса (он на фото справа), особенно про пересечение тактовых доменов, синхронные и асинхронные сбросы. А также материалы сайтов rtlery.com и zipcpu.com, особенно если у вас ограниченный опыт в промышленности. Еще пять материалов про арбитры, credit-based flow control и работе с памятью, которые помогут поднять тонус перед собеседованиями:

Credit Based Flow Control. Архитектура ЭВМ, Принстонский университет

Arbiters: Design Ideas and Coding Styles by Matt Weber

Generating fast logic circuits for m-select n-port Round Robin Arbitration

Building Multiport Memories with Block RAMs

Composing Multi-Ported Memories on FPGAs

Кроме тем, связанных с проектированием, и RTL, и DV инженеру нужно четко понимать, как работает симулятор, иначе вы будете плодить баги, связанные с гонками (race conditions) и различными результатами симуляции до и после синтеза (pre- and post-synthesis simulation mismatch). Из этого понимания следует правильная методология использования блокирующих и неблокирующих присваиваний, которая вскользь упоминается у Харрисов. На тему работы симулятора есть очень полезный Appendix вот в такой книжке, которую я тоже рекомендую:

Для инженеров, которые идут на позиции по design verification, я рекомендую проштудировать следующие три книжки от начала до конца.

В первой книжке (Chris Spear) по человечески описана coverage-driven constrained random verification methodology, а также отличия SystemVerilog от Verilog-95 и Verilog-2001 (если вы их учили в вузе). Без этой книжки вам придется копаться в стандарте, который во-первых написан более мутным языком, а во вторых не объясняет зачем нужны те или иные фичи языка.

Вторая книжка (Vanessa Cooper) - это короткий тьюториал по UVM, который можно изучить быстро. UVM не так широко используется в электронных компаниях, как утверждает маркетинг компаний, которые продают тулы, поддерживающие UVM. Но что такое UVM и с чем его едят должен в 2022 году знать каждый верификатор, так как шанс нарваться на кусок UVM-а в том или ином проекте существует. Только не копируйте из этой книжки шаблон писания драйвера шины - он совершенно не подходит для более сложных шин, типа AXI с конвейерностью и внеочередным получением ответов (для них нужно поддерживать табличку "транзакций в полете" и строить конечный автомат, использующий такую табличку).

Третья книжка (Janick Bergeron) описывает философию верификации и индустриальные практики. Если вы никогда не работали в команде верификации чипа или блока, эта книжка съэкономит время вас и ваших коллег, когда вы будете задавать им вопросы.

Помимо книжек есть полезные сайты, например www.testbench.in

Если у вас нет доступа к дорогим промышленным тулам для симуляции Synopsys VCS, Cadence Xcelium и платной Mentor / Siemens EDA Questa, то я рекомендую вам получить бесплатный доступ через сайт под названием edaplayground.com . Бесплатные тулы вне этого сайта (Icarus Verilog и бесплатная версия Questa) достаточны для тренировки решения интервьюшных задач на тему RTL, но в них нет поддержки covergroups, constrained random generation и concurrent assertions, чем необходимо владеть для позиций по DV.

Кстати о concurrent assertions, утверждениях темпоральной логики. Они в последние годы становятся важным инструментом не только инженеров-верификаторов (DV), но и инженеров -проектировщиков (RTL), особенно в связи с развитием тулов формальной верификации типа Jasper Gold. Эти тулы позволяют автоматически получать ответы на вопросы типа "допустим на входе в блок у меня такие-то сигналы установлены так-то. Следует ли из этого, что потом, через много тактов, на выходе будет (или не будет) то-то?" Тул автоматически проанализирует ваш RTL и ответит "увы, вот контрпример" и покажет сценарий, когда ваше предположение нарушается, например в логике участвует сигнал, который вы забыли.

Очень полезно для анализа чужого кода. Я вообще думаю, что вузы могли бы вводить такие тулы для обучения студентов в самом начале учебной программы, чтобы они сразу правильно ставили мозг на анализ событий в конвейерах и вообще сложных последовательностных схемах.

"А как же графика?" - спросите вы, - "ведь железо, которое я буду проектировать, предназначено для быстрого вывода на экран монстров в шутерах, не так ли?" Да, вам нужно будет в конце-концов изучить графику, начиная с софтверного API, посколько все эти объекты - треугольники, матрицы преобразований координат, плоскости для отрезания и т.д. будут приходить к вам в виде данных на шинах и всяких установок извлекаемых из регистров, в которые будет писать софтверный драйвер. Но это необязательно учить сразу. Сразу нужно уметь решать микроархитектурные задачки, писать на верилоге и понимать что такое статический анализ тайминга. А монстры и шутеры - это потом, в процессе.

|

|

В КНР появилась работоспособная альтернатива учебным FPGA платам от Intel/Altera и Xilinx/AMD |

Исторический момент! Александр Белиц запустил китайскую плату Tang Primer 20K с китайским же FPGA Gowin, освобождающим мировую общественности от зависимости от американских компаний Intel/Altera, Xilinx/AMD и Lattice (последний лично Трамп запретил продавать инвесторам из КНР). От зависимости по крайней мере на рынке образовательных FPGA плат, лабы на которых - стандартный элемент подготовки будущих проектировщиков микросхем ASIC внутри смартфонов, суперкомпьютеров, инфраструктуры интернета, быстрого AI для распознавания лиц террористов в толпе, кораблей бороздящих просторы вселенной итд итп.

Подвиг Белица был непрост - помимо кучи проблем с USB, у коннектора для платы не хватало проводка, плюс нужно было перепрошить firmware программатора (не путать с прошивкой FPGA) из бинарного файла, найденного на российском форуме electronix.ru. То, что большинство документации на китайском языке - это были сущие мелочи.

Теперь все это нужно задокументировать, опубликовать, спортировать на эту плату мои примеры и (если все будет выглядеть лучше чем у Интела/Альтеры и Xilinx/AMD) пересадить на Gowin будущих студентов моих семинаров.

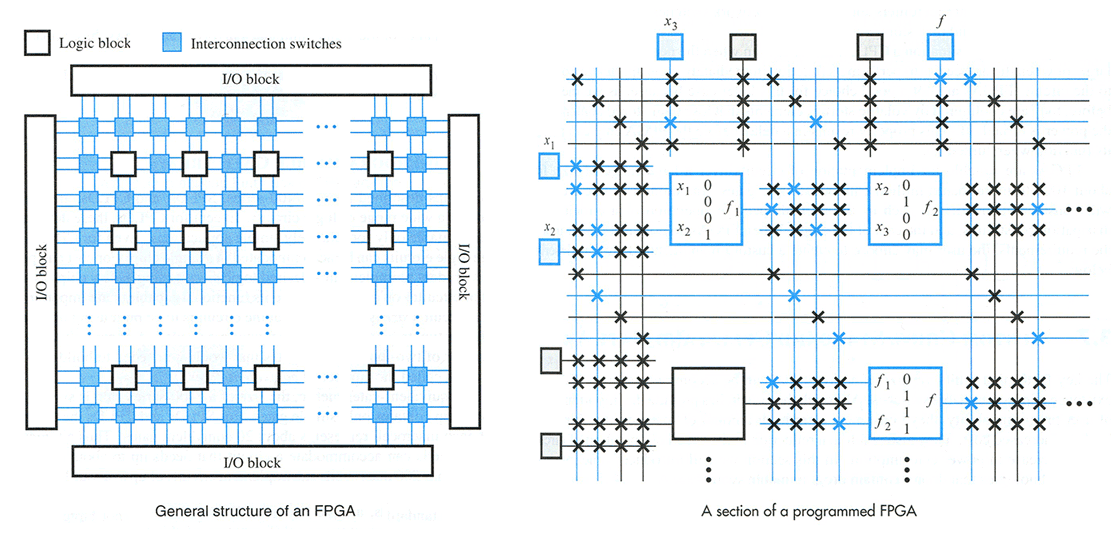

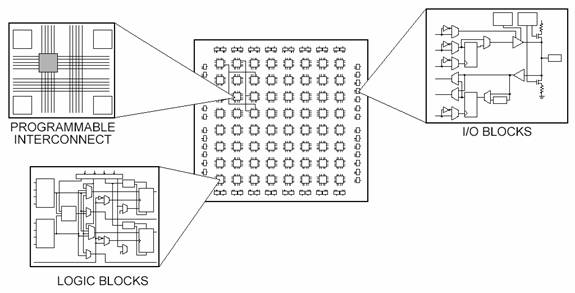

UPD: для тех, кто не знает что такое ПЛИС/ FPGA: это плата с микросхемой реконфигурируемой логики, пригодная для лабораторных работ типа курс MIT 6.111. Такие курсы проходят все будущие дизайнеры микросхем в айфонах итд. Внутри микросхемы Gowin на плате - матрица ячеек, логическая функция которых меняется с помощью изменения битов конфигурационной памяти. Это позволяет строить схемы типа учебных процессоров итд.

UPD2: для проектирования любой современной микросхемы - от микроконтроллера в кофеварке до системы на кристалле в смартфоне - требуются инженеры, которые владеют навыком проектирования на уровне регистровых передач с помощью языков описания аппаратуры (RTL Design Engineer). Это ключевой навык для команд проектирования процессоров, графических процессоров, сетевых чипов, нейроускорителей итд. Для тренировки таких инженеров изготавливать их учебные проекты на фабрике было бы слишком дорого. Поэтому их учат на FPGA, где можно описание схемы на языке описания аппаратуры Verilog превратить не в дорожки и транзисторы, а в прошивку конфигурационной памяти FPGA. В России команды RTL Design Engineers есть в таких компаниях как Байкал, Syntacore, Миландр (микроконтроллеры), Элвис (умные камеры) итд.

UPD3: пара скупых деталей для желающих повторить (потом сделаю пост на Хабре):

RV-Debugger-BL702.zip is downloaded from

https://electronix.ru/forum/index.php?app=forums&module=forums&controller=topic&id=166408&page=2#comment-1810016

bflb-mcu-tool-1.8.0.tar.gz is downloaded from

https://pypi.org/project/bflb-mcu-tool

cat /etc/udev/rules.d/99-sipeed.rules

SUBSYSTEM=="usb", ENV{DEVTYPE}=="usb_device", ATTRS{idVendor}=="0403", ATTRS{idProduct}=="6010", MODE:="0666", RUN+="/sbin/rmmod ftdi_sio"

К плате есть дополнительная периферия, про это будут дополнительные посты.

UPD4: для сравнения - introductory образовательная FPGA плата с чипом от Интел Terasic DE10-Lite стоит $135, от Xilinx/AMD - Digilent Basys2 — $165. Даже с учетом докупки дополнительной периферии плата с чипом от Gowin не хуже, сильно дешевле и схемы для нее быстрее синтезируются.

|

|

Беснование и опера в Сан-Франциско |

Сейчас в Сан-Франциско идет опера Евгений Онегин. Перед премьерой к зданию подошла художница Юлия Косивчук, которая принялась агитировать американцев туда не ходить. Выглядело это художественно, как имитация наркотического психоза:

Юлию охраняли два активиста, но оперу охраняли три охранника, поэтому вовнутрь она не прошла:

Помимо Юлии с комрадами, на протест пришла и другая группа людей, в составе 27 человек, которая вызвала у меня недоумение. Они несли украинские флаги, но украинцев среди них было очень мало.

Сначала я подумал, что это китайские студенты-воки, но потом заметил у них плакаты "буряты против войны". Ну хорошо, допустим, что буряты области сан-францисского залива беспокоятся о своих родственниках, попавших под мобилизацию в России. Но в этой толпе я заметил и человека с скорее латиноамериканской чем среднеазиатской внешностью.

Когда я поделился удивлением «что это за люди?» у себя на фейсбуке, мне рассказали, что у нас в Калифорнии оказывается есть компания, которая за небольшие деньги организовывает толпу для протеста на любую тему:

Других протестантов было немного - товарищ с громкоговорителем, который читал что-то по бумажке и семейная пара с жовто-блакытнымы флагами.

Несмотря на уверения протестующих, что «пока вы смотрите, Россия убивает», около трех тысяч американцев вошли в здание оперы чтобы посмотреть творение Пушкина и Чайковского.

Опера в Сан-Франциско большая, с несколькими ресторанами и барами. Многие зрители пришли заранее, чтобы пообедать свежайшим мясом, выпить вина и почитать программу:

В опере есть магазинчик с мини-музеем, в котором есть например про немецкого композитора Вагнера:

Пришел полный зал:

Опера оказалась неожиданно увлекательной. Я думал, что буду сидеть три часа с томлением "боже, прошло всего 20 минут", но реально действие захватывало внимание - это синтез хорошо структурированного повествования, стихов , музыки, пения, актерской игры, костюмов и постановки.

Как начинающий игрок на флейте я также посматривал когда в каких местах вступают флейтистки - их было три - первая, вторая и пикколо. В антракте я пошел посмотреть на флейтисток поближе:

Потом вышел в коридор:

И съел в буфете бутербродик:

В конце действа много хлопали:

В общем получилось очень душевно. Буду ходить на оперы еще.

Евгений Онегин будет идти в Сан-Франциско до 12 октября. Также рядом со зданием оперы есть здание филармонии. Там вроде собираются играть Чайковского, надо и на него сходить.

|

|

Начинать воевать на авось - дурацкое решение, но зачем еще и усугублять призывом на фронт R&D? |

Я долго думал, но все-таки не могу понять, почему россияне делают бронь для программистов и не делают бронь для электронщиков. Ведь и коню понятно, что реальное сражение идет не на поле боя, а в военном R&D. На поле боя - только окончательные тестировщики. У кого лучше Хаймарс - тот и прав. А историю потом перепишут под победителя. Вот Америка напала на Ирак в 2003 году (не путать с 1990) по выдуманной причине и против воли ООН - и хоть бы хны.

Согласно вот этому тексту, в Орлане стоит старинный первый Cyclone (я даже с детьми на лабах использую Cyclone-IV, хотя и он устарел), в Искандере стоит Xilinx 4000, из этой серии был мой первый FPGA в 1997 году итд. То есть там вообще-то обширное поле деятельности. Даже если текст по ссылке - фейк, есть масса других источников информации для такого вывода.

Американские военные контракторы, согласно докладу, который я слушал на DVCon, еще 10 лет назад использовали современные технологии верификации на SystemVerilog (в смеси с RTL на VHDL который по уставу положен военным), а в российских вузах ничему такому (functional coverage based constrained random verification итд) вообще не учат (в украинских вузах кстати еще хуже за некоторыми исключениями).

Сравнение зарплат военных электронщиков в Америке и России я проводить не буду - при ценах на дома в Silicon Valley американские военные контракторы тоже не жируют. Но американских по крайней мере не тащут в военкомат (местный военкомат называется Selective Service System - я сам состоял на американском военном учете в молодости. Вообще я успел состоять на военном учете в четырех странах - СССР, России, Украине и США).

RTL-щик, Design Verification или ASIC Physical Design Engineer с повесткой - это бред. Хоть с пацифистской, хоть с милитаристской точки зрения. Я просто не понимаю логику, может мне кто-то объяснит.

UPD: На ФБ мне задали вопрос "Mike Potanin А почему вообще возникла потребность "делать бронь" вопрос не возникает?"

Отвечаю: лучше бы вообще не начинали воевать, если уж начали - то только если есть возможность быстро вырубить высокоточными ударами вооруженные силы оппонента и объявить победу без жертв среди мирного населения, но если уж дошло до превращения городов в щебенку - на хрена еще и R&D свой резать - это же идиотизм, они хотя-бы FPGA дизайны могут улучшать с имеющимися вооружениями.

Также вышла статья по теме: Минпромторг импотент? Да.

|

|

AMD проводит суперкомпьютерный день в Казахстане. Можно подсоединиться по Zoom |

AMD проводит суперкомпьютерный день в Назарбаевском Университете в Астане, в Казахстане. 29 сентября. Можно подсоединиться по Зуму. Зарегистрироваться можно до 27 сентября по ссылке.

Вообще приезжающие в Астану замечали, что в городе есть амальгамация духа советских городов с духом американского Лас-Вегаса, в частности в элементах архитектуры.

Теперь можно добавить и другое сходство: в Лас-Вегасе помимо казино есть университет, в котором еще в допотопные времена стояли суперкомпьютеры и велись конкурсы на качество распознавания образов. Также там сейчас преподает Сара Харрис, соавтор известного учебника. Кроме этого в Лас-Вегасе иногда проводится конференция DAC по автоматизации проектирования электроники. Почему бы не превратить Астану в евразийский центр такого рода?

Расписание докладов суперкомпьютерного дня AMD в Назарбаевском Университете:

September 29th event agenda (Astana local time):

- 9am-10am: Timour Paltashev (AMD), "AMD Accelerated Platforms and OpenSource SW Ecosystem for Graphics, HPC and Machine Learning Application Domains".

- 10am-11am: Yuri Panchul (DDVCA.com), "Digital Design and Verification in Central Asia: A project to integrate Central Asia into the World's Electronic Industry" (a remote presentation from California)

- 11am-noon: Pavel Stanavov (AMD), "AMD Computing Platforms for HPC and Data Centers in Exascale Era".

- Noon-1pm: Lunch Break.

- 1pm-2pm: Konstantine Voron (AMD), "AMD solutions: How to Secure and Build Your Own System".

- 2pm-3pm: Timour Paltashev, Nursultan Kabylkas (AMD, NU, UCSC),"Cooperation with Academic Institutions in AMD ROCm Ecosystem Tools and Libraries Development".

Вот как университет выглядит внутри:

Организатор семинара от AMD - архитектор компьютерной графики и высокопроизводительных вычислений Тимур Палташев, на снимке справа, во время планирования одного из предыдущих семинаров, в Томском Университете:

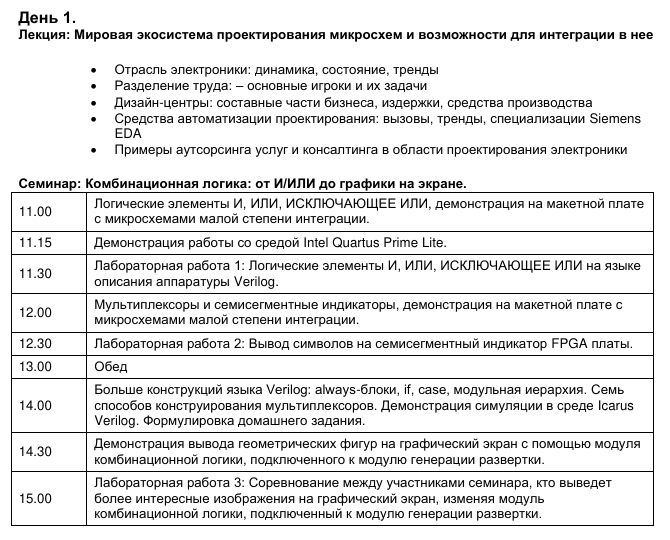

Тимур Палташев также помог организовать августовский семинар в Бишкеке, Кыргызстан. Это был первый семинар из серии Digital Design & Verification in Central Asia - "Цифровое Проектирование и Верификация в Средней Азии". Материалы семинара выложены на сайт ddvca.com и включают в себя видео и слайды лекций, релиз лабораторных лабот с FPGA платами и проверочных тестов, а также рассказ о существующих проектах по проектированию цифровых схем в Средней Азии.

Еще семинар в Бишкеке поддержало отделение Сименса, которое занимается автоматизацией проектирования электроники - Siemens EDA (ранее оно было компанией Mentor Graphics). Вот Денис Лобзов из Siemens EDA ведет презентацию в Бишкеке:

Целями семинаров DDVCA является:

- Быстрое введение в область проектирования цифровых микросхем для программистов, бизнесменов и продвинутых школьников матолимпиадного типа.

- Отработка материалов (слайды, лабораторные работы, экзаменционные задания) которые могут быть включены в стандартные вузовские курсы цифровой схемотехники и компьютерной архитектуры.

- Начальная тренировка сотрудников компаний, которые хотят расшириться в области, требующие понимания проектирования на уровне регистровых передач (Register Transfer Level - RTL), с использованием языков описания аппаратуры Verilog и VHDL, а также технологий функциональной верификации (SystemVerilog) и эмуляции.

Примеры организаций, для которых может иметь смысл участие их сотрудников в семинарах:

- Разработчики измерительных устройств с комбинацией встроенных процессоров и микросхем реконфигурируемой логики ПЛИС / FPGA.

Пример: система раннего оповещения о землетрясениях может использовать ПЛИС не только для интеграции микропроцессоров и сенсоров на печатной плате, но и для подавления высокочастотного шума и обнаружения сейсмических событий в быстро наступающей продольной волне.

- Компании, которые занимаются аутсорсом разработки программного обеспечения для глобальных заказчиков. Они могут расширится в область аутсорса разработки тестов и моделей блоков систем на кристалле (System on Chip - SoC) для микроэлектронных компаний.

Пример: крупная корейская электронная компания SK Hynix создала восточноевропейский центр для верификации своих контроллеров флэш памяти.

- Университеты, которые хотят создать у себя группы по разработке инновационных вычислительных устройств, особенно в области аппаратных ускорителей машинного обучения и трехмерной графики.

Пример: процессор Leonhard для обработки множеств, структур данных и графов, спроектированный в Московском государственном техническом университете им. Н.Э.Баумана.

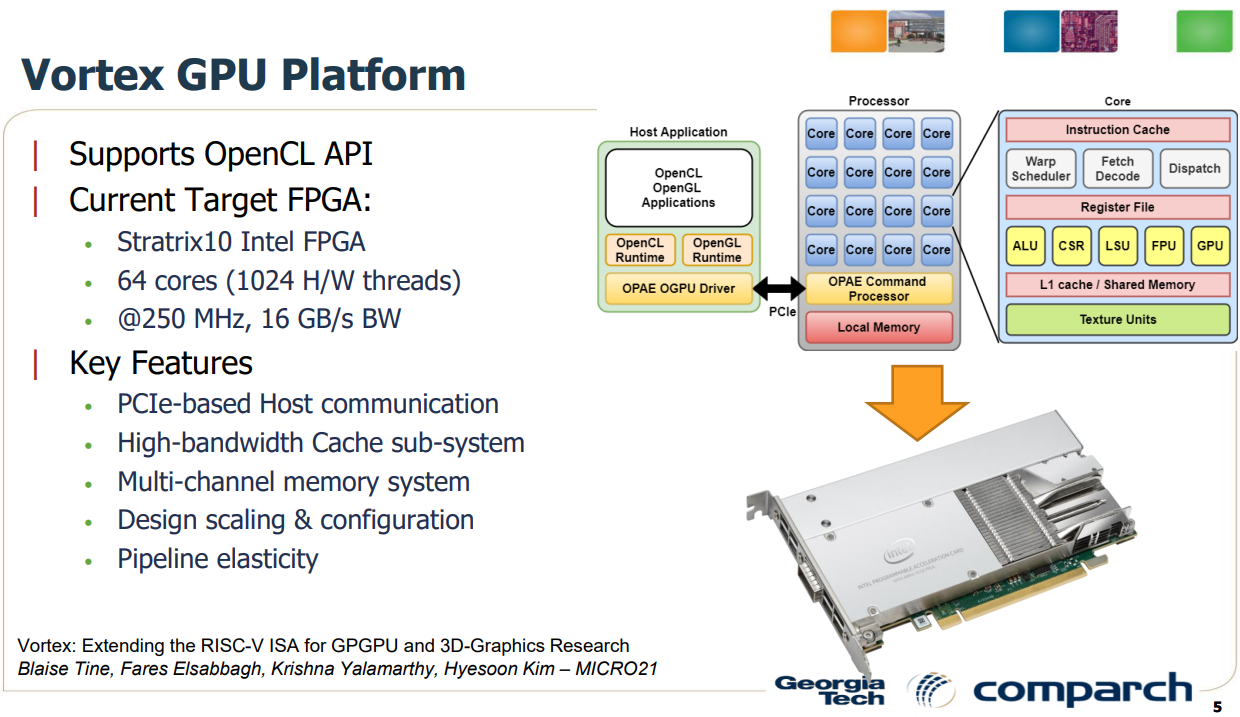

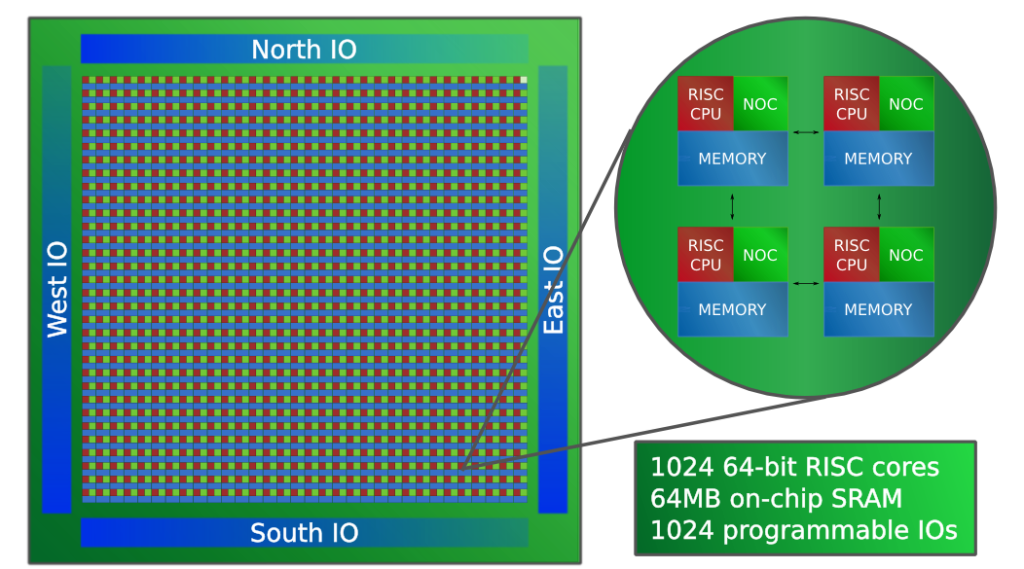

Другой пример: группа в Georgia Institute of Technology, которая создала открытый Vortex GPU. Этот графический процессор построен на основе решетки из небольших процессорных ядер с архитектурой RISC-V. Архитектура ядер расширена инструкциями для аппаратной поддержки многопоточного выполнения внутри каждого ядра, а в микроархитектуру добавлены дополнительные наборы регистров, по набору для каждого потока.

Оба устройства, бауманский процессор и GPU из Джоджии, спроектированы в форме описания на языке Verilog и прототипированы на платах FPGA.

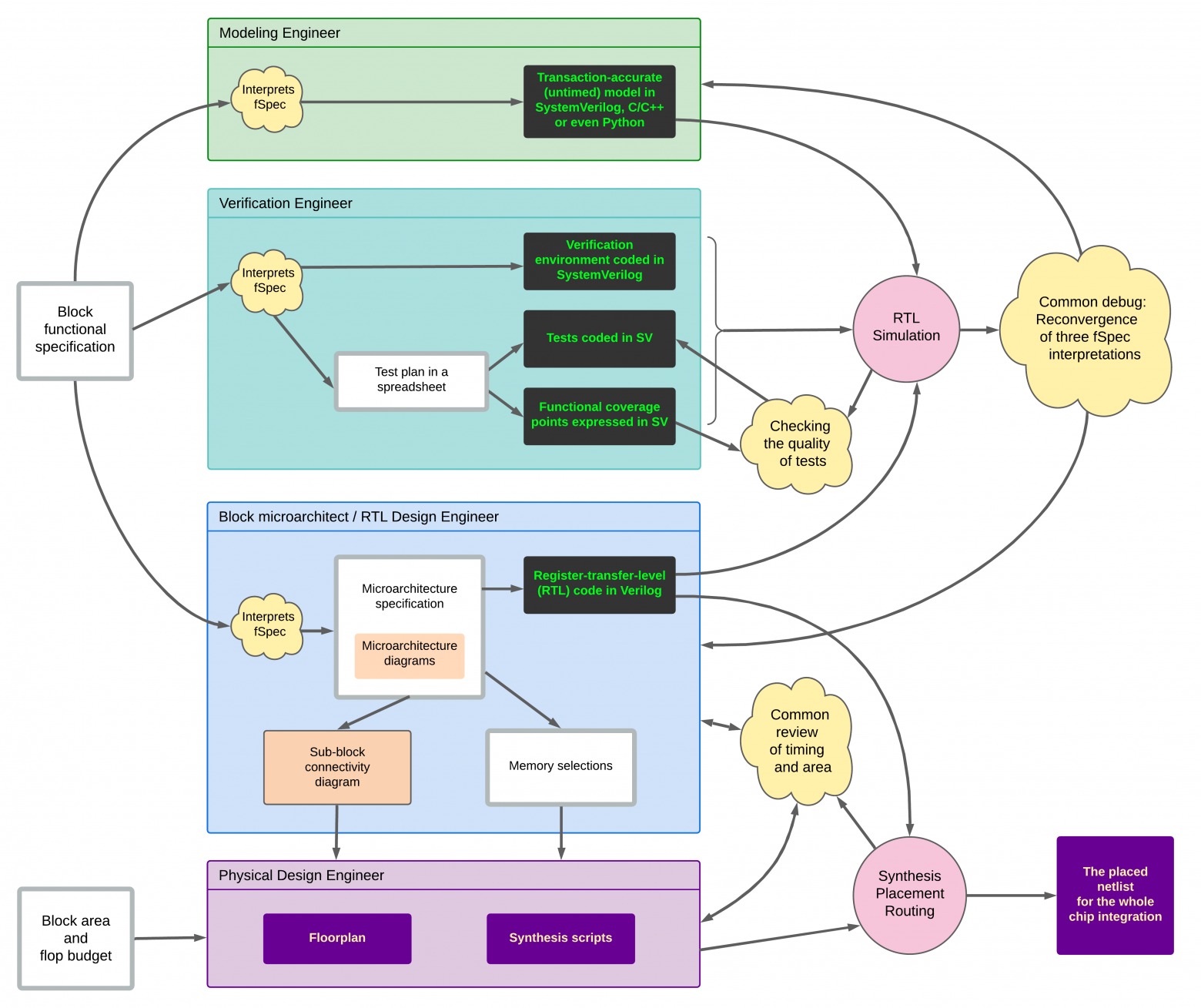

На суперкомпьютерном дне в Нурсултане в докладе о DDVCA будет в частности рассказ о том, как организовано проектирование чипов в электронных компаниях Кремниевой Долины, восточной Азии и Западной Европы. И какие части этого процесса могут начать аутсорсить команды в Средней Азии.

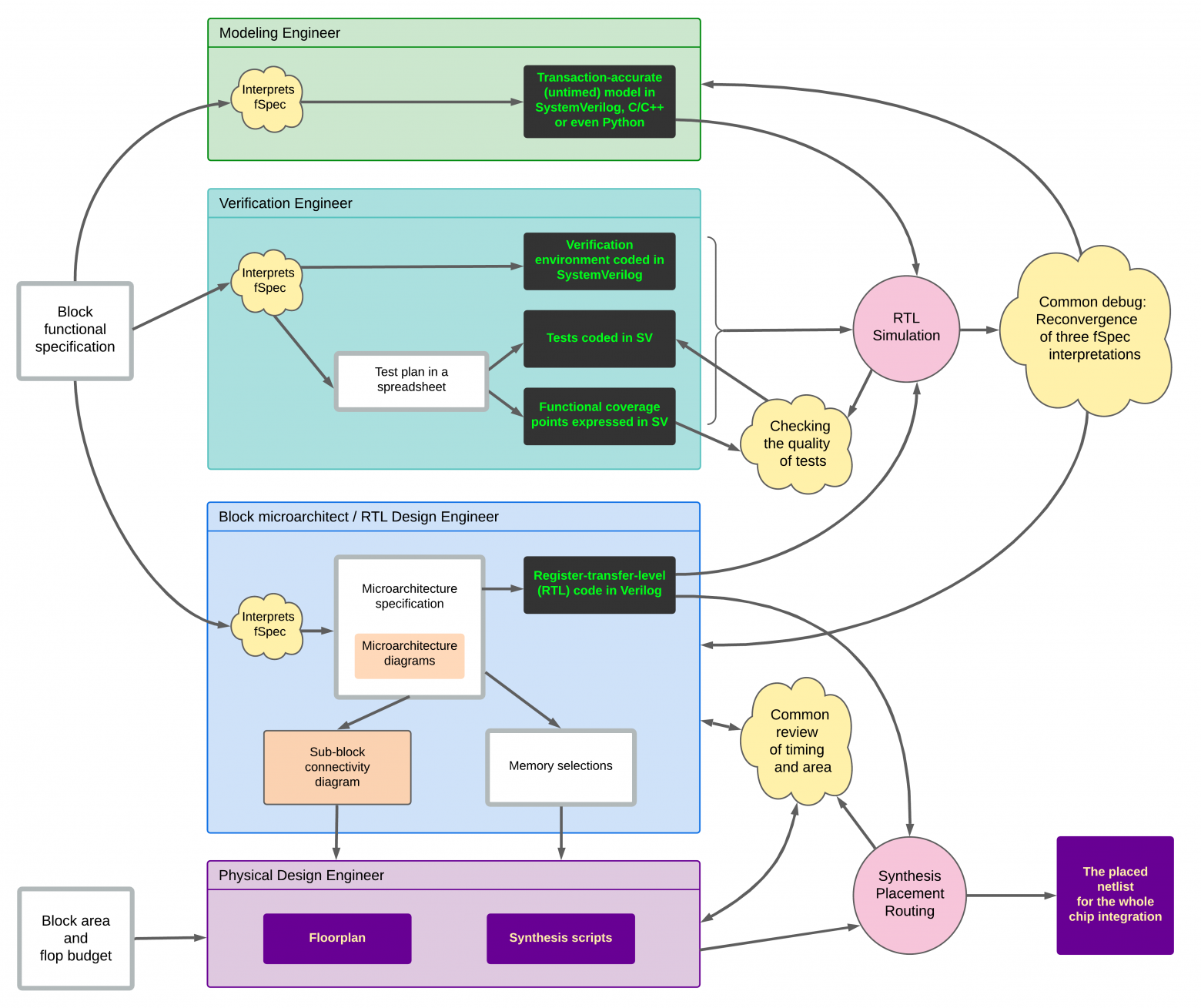

Команда проектирования чипа крупным планом:

А вот команда проектирования блока. В чипе или в semiconductor IP (которое само по себе является большим блоком) могут быть десятки разных типов блоков. Каждый блок может состоять из миллионов транзисторов и размещаться в чипе много раз, для параллельной обработки данных. Команда блока состоит из инженеров из разных отделов: логического проектирования, верификации и физического проектирования.

В общем, регистрируемся и думаем на каверзными вопросами для обсуждения. 29 сентября будет интересный день. Во время презентации мы также обсудим следующие семинары в Средней Азии, которые уже планируются.

|

|

Русский язык как Си и украинский как Bash |

Книжку издательства Мир по Bourne Shell я читал еще в автобусе в Киеве в 1986 году. Но до сих пор, когда пишу даже маленький башевский скрипт, все время куда-то заглядываю. Раньше в книжку, теперь в stackoverflow.

Так и с украинским. В детском саду был украинский, в школе украинский язык и литература. Марко Вовчок, Панас Мырный, Иван Франко, Остав Вышня с его несмешным юмором, даже книжки по математике на украинском читал - но все равно, как надо что-то написать, приходится подглядывать в словарь.

Я не одинок. Мне рассказывал один бывший преподаватель украинского вуза, что в современной Украине многие статьи на украинском пишутся с помощью перевода Google Translate-ом текстов на русском, без афиширования данной технологии.

Частично это связано с тем, что националисты импортируют в язык новые слова, чтобы отдалить его от русского. Например вот ввели слово "нацюцюрник". Не было такого слова в украинском в моем детстве! Мы говорили просто "гандон".

Население, большая часть которого экзамен по украинскому не сдаст, переиначивает русские слова и получается как итальянский в мультфильме "Приключения капитана Врунгеля": "мы бандитто, гангстеритто, банко тресто миллионно и плеванто на законно".

Короче, я это все к чему. Я написал скрипт на Баше для генерации пакета для семинаров в Средней Азии. Скрипт копирует файлы для примеров из одного источника, создавая дубликаты. Это нужно чтобы не взрывать мозг студентам, чтобы они всегда видели простые файлы в локальной директории примера, и не лезли в другие директории, чтобы не было лишних инклудов, врапперов итд.

Прошу критиковать:

https://github.com/ddvca/2022-bishkek/blob/main/scripts/prepare_package.bash

|

|

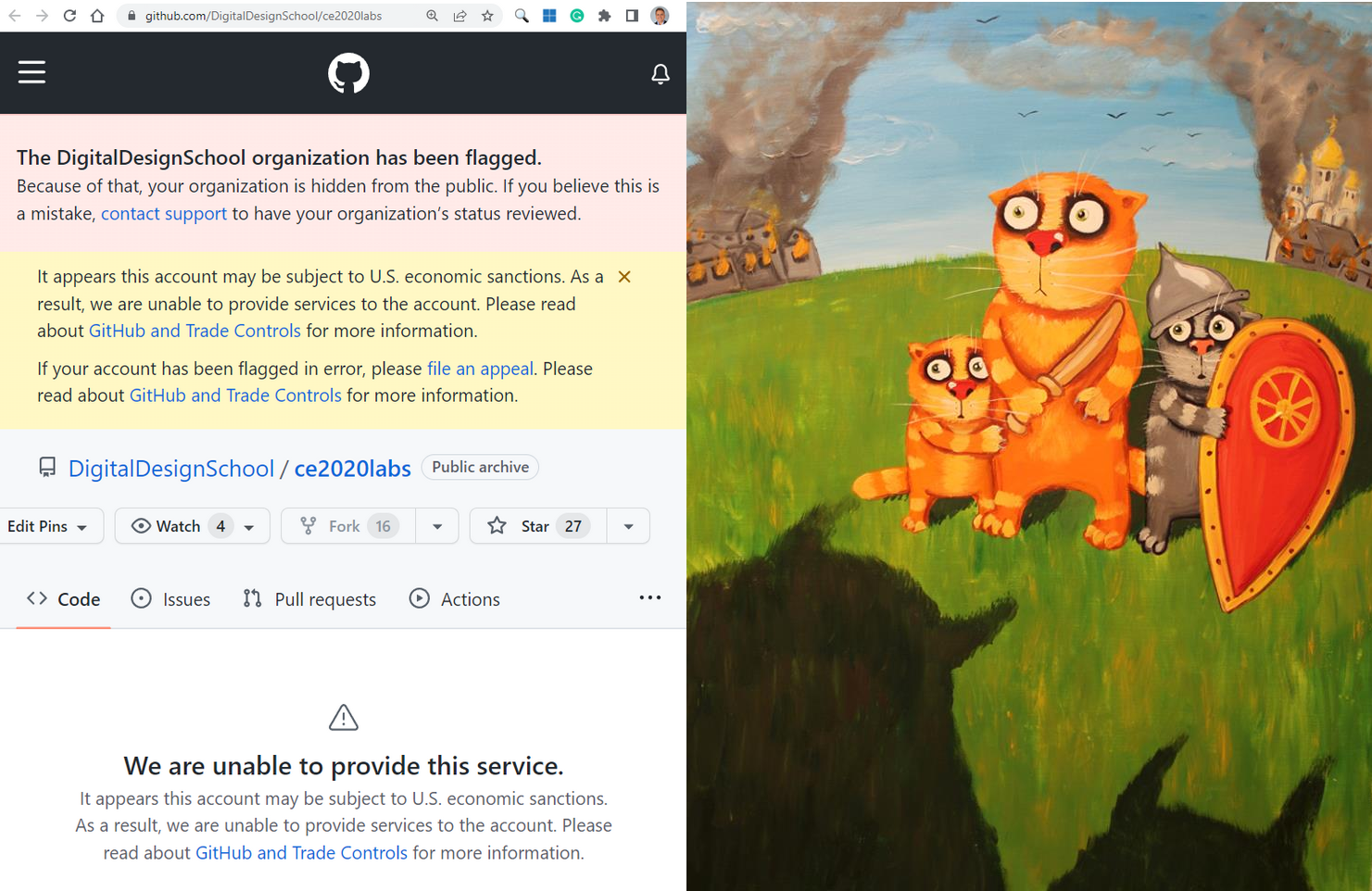

Как я выиграл апелляцию против американских санкций |

В прошлое воскресенье 4 сентября я обнаружил, что GitHub-организация DigitalDesignSchool, в которой я являюсь одним из владельцев, забанена Гитхабом с формулировкой "ваш аккаунт может быть предметом американских экономических санкций".

Пораскинув мозгами и посовещавшись с моим приятелем, основателем московского интернет-провайтера RiNet Сергеем Рыжковым, у которого в тот же день забанили счет в Ситибанке в Лондоне, я решил: нужно бороться.

Сначала я изучил страницу GitHub and Trade Control, на которой нашел несколько занятных вещей. Например, оказывается GitHub получил разрешение от U.S. Treasury Department's Office of Foreign Assets Control (OFAC) оказывать услуги разработчикам open-source проектов в Иране. Также оказывается GitHub агитирует американские органы ослабить ограничения на Крым и Сирию в честь прогресса человечества и свободы слова:

GitHub will continue advocating with U.S. regulators for the greatest possible access to code collaboration services to developers in sanctioned regions, such as Syria and Crimea, including private repositories. We believe that offering those services advances human progress, international communication, and the enduring U.S. foreign policy of promoting free speech and the free flow of information.

Когда я это прочитал, я понял, что надо не ходить с кислой рожей, а помочь прогрессу человечества и подать на апелляцию против бана DigitalDesignSchool, тем более что это моя гитхаб-организация.

Поэтому я нажал на кнопку подачи апелляции, где было много вопросов, кто состоит в организации и чем она занимается и одновременно создал тикет в поддержке Гитхаба со следующим текстом:

Hello: I got a message that my organization DigitalDesignSchool was flagged and hidden from the public.

I am the owner of this organization and I am a US citizen so I could not be under the sanctions.

I guessed this issue happened because the description of the organization references Skolkovo which is under sanctions.

However, the organization itself is not a part of Skolkovo. There was a seminar on which the presenters rented a room in Skolkovo.

So Skolkovo was used for marketing purposes and that was it.When I tried to remove the Skolkovo reference from the account, I got a message "It appears this account may be subject to U.S. economic sanctions. As a result, we are unable to provide services to the account. Please read about GitHub and Trade Controls for more information."

Please review the status of the account. It has a set of basic Verilog examples used for seminars in many places - not only in Russia but also in Ukraine, Kazakhstan, Kyrgyzstan - worldwide. It is a pity if mentioning Skolkovo once because of a past seminar jeopardizes basic Verilog learning for many people.

Thank you,

Yuri Panchul

Одновременно я начал изучать альтернативы GitHub-у: GitLab, Gitee и Bitbucket. Из них мне показался самым перспективным Gitee, который находится в Китайской Народной Республике. В процессе изучения GitLab и Gitee я обнаружил новые для меня фичи CI/CD с использованием YAML (не делайте рука-лицо, я писатель на верилоге, а не DevOps), так что из инциндента я даже извлек некую для себя пользу.

Но пока суть да дело, суппорт GitHub-а посовещался со своими юристами и они решили меня разбанить. Сначала мне пришел такой емейл:

GitHub and Trade Controls

From: GitHub Trade AppealsThank you for submitting additional information regarding the trade restrictions placed on your GitHub account. Based on the information you provided, we have enabled full service on your account.

We appreciate your patience and cooperation during this compliance process.

Please note that your organization and/or user account may be flagged again in the future if our system determines the organization is based out of, or the key individuals or membership of the organization shows sufficient ties to, a sanctioned jurisdiction, or if the organization otherwise appears to be restricted by U.S. economic sanctions.

а потом такой:

GitHub (GitHub Support)

Hi Yuri,

Thanks for reaching out to us with these details, and the details you shared through our appeals form. After a legal review we have lifted restrictions on this organization. You should now be able to resume normal GitHub use.

To avoid future difficulties I will recommend you remove any references to Skoltech now that you can access your profile again.

Thanks for your patience during this process.

Regards,

GitHub Support