������������ ����������� ����� � ModelSim |

�������� ������ FPGA/����������� ���������� �� ajrec.

� ������ �������� � ������ �� �����, � ����� �������� ��� ��� � ����� ������ �� �����. �� ����� ���� � �������� ��� ��� ������ ajrec ��� ����������� ����� � ������ ��������������, ��� ���� �������, ��� ��� ������ ����� (���� ������, ��� ���� �������������� � FPGA � ���� ����).

� ������������ � ������� ����� � �������� �������� ������, ����� ������������ � ������� ��� �� �� ��������, ��� � �.

������ ������, � ������ � ������������ ������ �� �������, ������� ��� �����, ��� ���. � ������, ��� ������ ����� ������� ����� ���� ���� ������� �����������, ���� ������ ��������. ���� ������� ���-�� ��� ��, ��� � ����� ������ �������������, �� ����� ����������� �������, ����� ����� � ���������. ������� ��� � ������� � ����� ����� ������ ����� ������ �� ���.

� ���������� ����������� � ������� ������������ ����������� � �� ������� ���� ������� ��������� ��������� ���� � ModelSim. ����� � ���, ��� �� ����� ����������.

������ ������, ���������� � ������ "����������� ����������" � "������� ������� �������������� ���� Petrify: �������� � �� �������" ����� ������ � ��� ������. � ������������ ��������� ��������� ����������� �������.

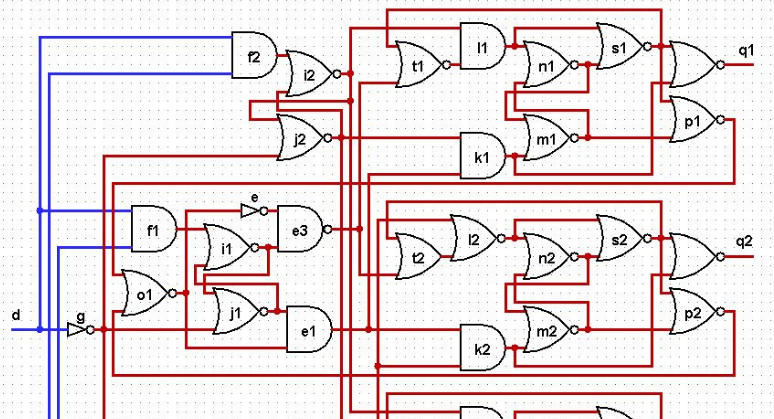

����� ����, � ������ ���� ����������, ������� ����� ����. ���, ��������, ������:

�������� �������:

q1 � ������������� ���� r1=1 � r2=1;

q2 � ������������� ���� r1=1 � r2=0;

q3 � ������������� ���� r1=0 � r2=1;

q4 � ������������� ���� r1=0 � r2=0.

� �������� ����������, �� � ������ ����������� ���� ������������, ������� ����� ��������� �������� ������������ � ������� � ����� q4 �������������, ����� r1=0 � r2=0. � ���� ������ ��� ������ �� �������: { 0, 0 } � ������������� ������� q0. { 0, 1 } � ������������� ������� q1. { 1, 0 } � ������������� ������� q2 � { 1, 1 } � ������������� ������� q3. �� ���, �������, ������, ������� �� ��������� � ����.

�������� �� ��������� � ���� �������: ����� �� ��������� ���� ��������/������������/������� � ���� ��� ����� ������ ��������. �� �����: �� ���� ��� ����������� ��������� ����� � �������� ����������.� �� ��� ��� ��?

���������� ��� � ����������� ���� � ����� ����������� ��������������� ������ ���������� ajrec �����������. ��������� ��������� � ��� ���������� ������� ������, ������� ����� ���������� ��������� ����� � �������� ����. ������� ��� ���� ����� � � ���� ��� ������ �����������, ��� ModelSim ������ ���������� ������������ ����������� �����: ��������� ModelSim ������������ ������ ����� ��� �������������� ����������� �������.

����. �������� ��� �� ������ FPGA/����������� ���������� � ��� �� ���� �� ����� ����� � �������� ��������� �������:

e=NOT(o1); e1=AND(o1,j1); e2=AND(o2,h1); e3=NAND(e,i1);

e4=OR(o2,h1); f1=AND(d,r1); f2=AND(d,r2); g=NOT(d);

h1=NOR(g,r1); h2=NOR(g,r2); i1=NOR(f1,j1); i2=NOR(f2,j2);

j1=NOR(g,i1); j2=NOR(g,i2); k1=AND(e1,j2); k2=AND(e1,h2);

k3=AND(e2,j2); k4=AND(e2,h2); l1=AND(t1,i2); l2=NOR(t2,h2);

l3=AND(t3,i2); l4=NOR(t4,h2); m1=NOR(k1,n1); m2=NOR(k2,n2);

m3=NOR(k3,n3); m4=NOR(k4,n4); n1=NOR(l1,m1); n2=NOR(l2,m2);

n3=NOR(l3,m3); n4=NOR(l4,m4); o1=NOR(p1,p2); o2=NOR(p3,p4);

p1=NOR(m1,s1); p2=NOR(m2,s2); p3=NOR(m3,s3); p4=NOR(m4,s4);

s1=NOR(n1,l1); s2=NOR(n2,l2); s3=NOR(n3,l3); s4=NOR(n4,l4);

t1=NOR(e3,s1); t2=OR(e3,s2); t3=NOR(e4,s3); t4=OR(e4,s4);

q1=NOR(s1,k1); q2=NOR(s2,k2); q3=NOR(s3,k3); q4=NOR(s4,k4).����� � ������ ���� ������������� ����� ���� ����� � ��������� � ���, ��� ������-�� ������� m1, m2, m3, m4 ����� ��� ���������� � �������� ��������� ����� ������� ������. ������, �������� ��� ��� �� ���� Verilog ��� ���:

module test(

input wire d,

input wire r1,

input wire r2,

input wire set0,

output wire q1,

output wire q2,

output wire q3,

output wire q4,

output wire [3:0]qq

);

wire e, e1, e2, e3, e4;

wire f1, f2;

wire g;

wire i1, i2;

wire j1, j2;

wire h1, h2;

wire k1, k2, k3, k4;

wire l1, l2, l3, l4;

wire m1, m2, m3, m4;

wire n1, n2, n3, n4;

wire o1, o2;

wire p1, p2, p3, p4;

wire s1, s2, s3, s4;

wire t1, t2, t3, t4;

function NOT;

input s;

begin

NOT=~s;

end

endfunction

function AND;

input s1,s2;

begin

AND=s1&s2;

end

endfunction

function NAND;

input s1,s2;

begin

NAND=~(s1&s2);

end

endfunction

function OR;

input s1,s2;

begin

OR=s1|s2;

end

endfunction

function NOR;

input s1,s2;

begin

NOR=~(s1|s2);

end

endfunction

assign e=NOT(o1); assign e1=AND(o1,j1); assign e2=AND(o2,h1); assign e3=NAND(e,i1);

assign e4=OR(o2,h1); assign f1=AND(d,r1); assign f2=AND(d,r2); assign g=NOT(d);

assign h1=NOR(g,r1); assign h2=NOR(g,r2); assign i1=NOR(f1,j1); assign i2=NOR(f2,j2);

assign j1=NOR(g,i1); assign j2=NOR(g,i2); assign k1=AND(e1,j2); assign k2=AND(e1,h2);

assign k3=AND(e2,j2); assign k4=AND(e2,h2); assign l1=AND(t1,i2); assign l2=NOR(t2,h2);

assign l3=AND(t3,i2); assign l4=NOR(t4,h2);

assign m1=NAND( set0, OR(k1,n1)); /* NOR(k1,n1); */

assign m2=NAND( set0, OR(k2,n2)); /* NOR(k2,n2); */

assign m3=NAND( set0, OR(k3,n3)); /* NOR(k3,n3); */

assign m4=NAND( set0, OR(k4,n4)); /* NOR(k4,n4); */

assign n1=NOR(l1,m1); assign n2=NOR(l2,m2);

assign n3=NOR(l3,m3); assign n4=NOR(l4,m4); assign o1=NOR(p1,p2); assign o2=NOR(p3,p4);

assign p1=NOR(m1,s1); assign p2=NOR(m2,s2); assign p3=NOR(m3,s3); assign p4=NOR(m4,s4);

assign s1=NOR(n1,l1); assign s2=NOR(n2,l2); assign s3=NOR(n3,l3); assign s4=NOR(n4,l4);

assign t1=NOR(e3,s1); assign t2=OR(e3,s2); assign t3=NOR(e4,s3); assign t4=OR(e4,s4);

assign q1=NOR(s1,k1); assign q2=NOR(s2,k2); assign q3=NOR(s3,k3); assign q4=NOR(s4,k4);

assign qq = 1 << {r2,r1};

endmodule

� ���������� � �������� ��� ������� ����������� ���������, ����� �������� �� �������� ������, ������� � �� �������. ������� � ��������� Verilog ������� AND, OR, NOR, NAND, ����� ��� ������ ��, ��� ������ ������. ���������� �������� ������� � Verilog �������� ����� assign. ���� ���� �����, �� ��� ������� �������� ����� Verilog.

����� �������, � ������ test ������� ������� ������� ������������� ������ r1 � r2, � ��� �� ������ ������ set0 � ������ d � ������� �� �������� ���������� ������ (� ������������ ������). �������� ������� q1, q2, q3 � q4.

����� �����, � ������� ����������, ������������� �������� ������ qq, ������� ����������� ������������ ������������, ��� ���: assign qq = 1 << {r2,r1};

������ test ��� �������� � ������ Intel Quartus Prime Lite Edition v16.1 ��� ���������� ���� Cyclone IV E.

������ ��� �������������. �������������� � ���������� ������� Assignments=> Settings => EDA Tools Settings => Simulation ����� ������� Tool Name => ModelSim-Altera. �����, ����� ���������� ����� ������� ����� simulation/modelsim � ������� ����� ���������� ������ *.sdo � *.vo, ������� ����� ��� ��������� ���������.

������ ����� testbench. � ������� ��� �� ��������:

`timescale 1ns / 1ns

module tb();

reg r1_;

reg r2_;

reg d_;

reg set_;

wire q1_,q2_,q3_,q4_;

wire [3:0]qq_;

test test_inst(

.d(d_),

.r1(r1_),

.r2(r2_),

.set0(set_),

.q1(q1_),

.q2(q2_),

.q3(q3_),

.q4(q4_),

.qq(qq_)

);

initial

begin

$dumpfile("out.vcd");

$dumpvars(0,tb);

//reset m1-m4 signals using "set_"

r1_=0;

r2_=0;

d_=0;

set_=0;

#100;

set_=1;

#100;

//check addr 00

r1_=0;

r2_=0;

#100;

d_=1;

#100;

d_=0;

#200;

//check addr 01

r1_=1;

r2_=0;

#100;

d_=1;

#100;

d_=0;

#200;

//check addr 10

r1_=0;

r2_=1;

#100;

d_=1;

#100;

d_=0;

#200;

//check addr 11

r1_=1;

r2_=1;

#100;

d_=1;

#100;

d_=0;

#200;

//--------------------

//check addr 00

r1_=0;

r2_=0;

d_=1;

#100;

d_=0;

#200;

//check addr 01

r1_=1;

r2_=0;

d_=1;

#100;

d_=0;

#200;

//check addr 10

r1_=0;

r2_=1;

d_=1;

#100;

d_=0;

#200;

//check addr 11

r1_=1;

r2_=1;

d_=1;

#100;

d_=0;

#200;

end

endmodule����� ������� ������� r1 � r2 ���������� ��������������� �� ��� ������ ��������� �������� 2'b00, 2'b01, 2'b10 � 2'b11, ��� ���� ��� �������������� ���� ������ d, ������� ������������ �������������.

��� ��� ���������� ��� ����, ������ ������ ������ ������� ��������� ���������� d ���������� ��� �������������� �������� r1 � r2, � �� ������ ������ �������� d �������� ������������ � ��������� r1 � r2. ������ ������ � �� ����, ��� ��� �� ����� ���� ������ ���� �� ������� ������. ������ �� ����� � ������������ ��� ����� ������� ������, ������ ������� ��������� d � ������ ������������ �������� r1 � r2.

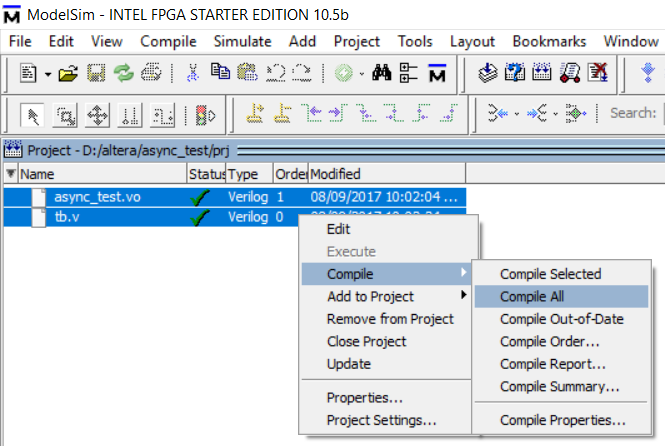

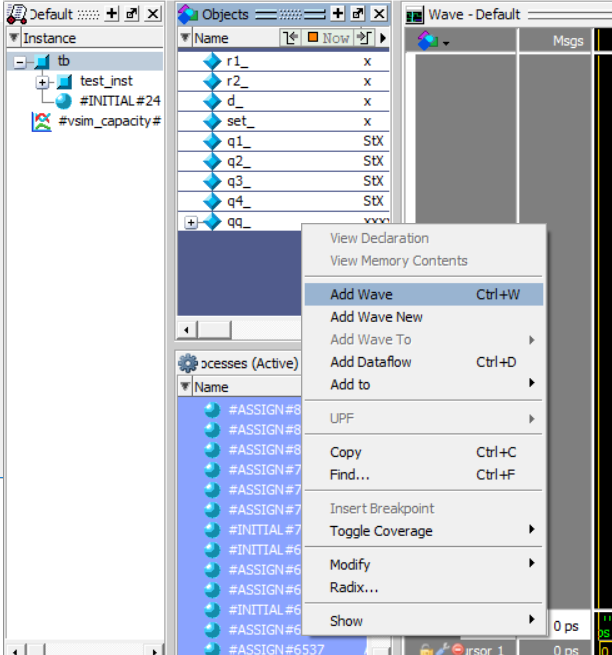

������ �������� ModelSim-Altera (��� ������ ��� Intel). ������ ������ � ���������. �������� � ���� ��� ������������ �����: �������� tb.v � ���������������� ��������� ������ async_test.vo:

�� ������ ��� ����� ��������������� ��� � ������� ModelSim. ������ ������ ���� � ������� �� ���� Compile All. ����� ����� ��������� ������� ���-����� ����� ������� �����. ������ ������ ���������� � ModelSim ������� �������������� ������ ���, ��� �� �� ����� �������. ��� ���, � �����.

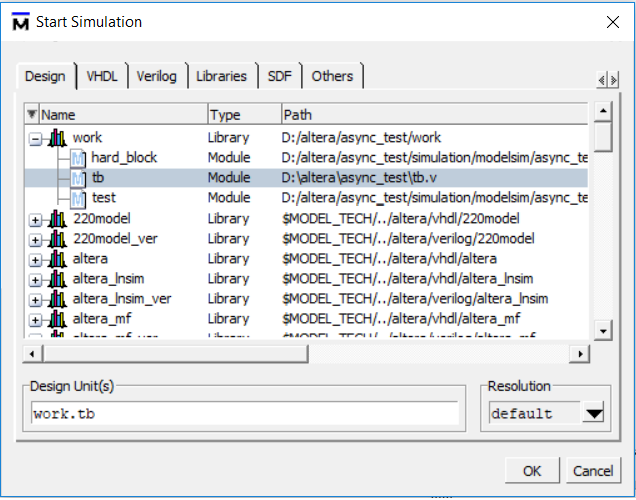

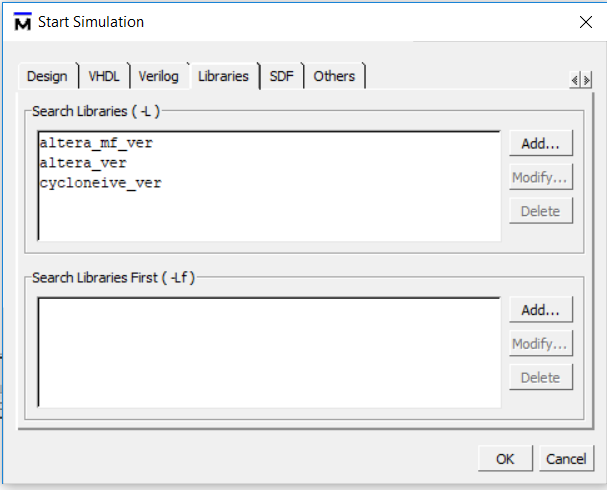

������ ����� �������� ��������� ����� ���� ModelSim, Simulate-> Start Simulation�

��� ���������� ���������� ���� ��� �����:

1) ������� ��� ������ � ������ ��� ��������

2) �������� ���������� �������

3) �������� ���������������� SDF ����, �� �������� ��� ��������� ��������� ������

����� �������� ��������� ���� ������ ��� ��������� ������ � ������� ����� �������� ������������ ��� ������� � ���� ��������� ���������.

�������� OK � ����� ���� Simulate => Run => Run-all

��� ��� � ���������� � ����������!

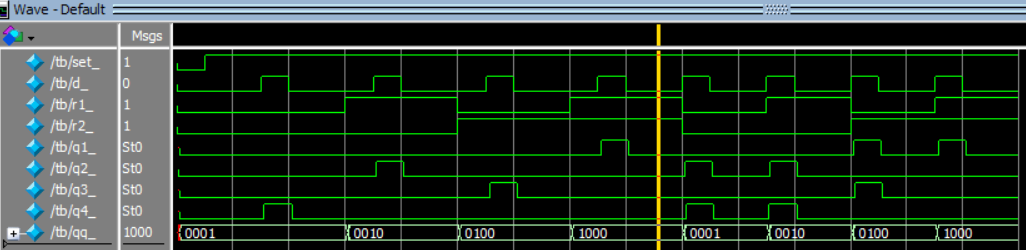

��� � ����:

��-������, ������ ������ ����� �������� � ���������� ������, ��� � ������� � ��� ������ ��� ������ ������ ������� ��������� d. ���-�� ���������� ������ �����������, ��� {r2,r1} = 2'b01 ���������� q2. �� � ��� ��� ���������� ���� ��� �������. ������ ������, � ��� ������ �������, ��� ��� ������ �������� ��� �����-�� ��������.

������ ������ �� 4� ��������� d �� �������� ���������. ��� ��� ������ ����� ������ d �������� ������������ � ������������� r1 � r2.

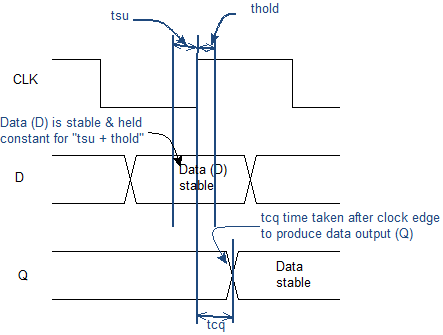

����� �������� �� ������ ������ ���� ������� d. � ���������� ������ � ���� ���� �������� �������, ������� ����������� ������ ��������� �� ������ �������� � ������� ����� �������������� �������. ��� ���� ����������� ������ ���������� ��� ���������� ��������� ��������� tsu � thold. ��� ������ ���������� �������� �� ���� �� �����:

������������� � �������� ������ ������ ���� ���������� ��������� ����� tsu (setup time) �� ������ �������� ������� � ��������� ����� ����� ������ �������� ������� thold (hold time). ���� ��� ������� �� �����������, �� ���������� ����� �� �������� ��� �������� �� ������� (�� �� ���� ���������� �� ��������).

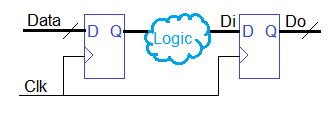

��� ����� ���������� ������? ��� ���� �������, � ������� ������������ ������� ������. ����� ���� ���������� �������, ������� �� ������� ������ (��� ����� ���� ��������� ��������) ��������� ��������� ��������, ������� ������������ � ��������� ��������. ��� ��� ���������� ������� ������ ��������� ��������� �� ����� �������, ��� ������������ ������� �������� �������. �� ������ ������ ���������. ��������� �������� ���������, �� ��������� ��� ������ ������ ������� ��������� �� ����������� ������ � ������ �������������� ��������.

������, ����������� � ����������� ����� � ������� d � �������, ��� ������ ������ �� ������� ��������� d � ���� ����������� ����� �� ����� ��������� ������ �� �������� ��������� ����� �� ��� �� �������, �� ������� ����� �� �������� � ���������� �����. � ������, �� �������� tsu. ������ d ��������, ����� ������� r1 � r2 ��� �� ������ ��� �� ���������.

��� �������, ��� ������ ����������� ����� �� ������� �������� ���������� �������. ����������� ����� ������������ � ������������ �������� r1 � r2 �� ������� d. ��� ����� ���-�� �������������� � ���������. ������ ������, ��� ������� d ���-�� ���������� ������������� �������� �������. � ������� d ���� ������������, ������ ���, ��� ������������ ���-�� ����������, �����-�� �����������? ����������, ��� ��� ������ ����������� ����� ��� ���� ����� ������������� ����, �� ������� ���������� ������������ � ������� ������ d? ������, ������������� ����� ������� d �� ����� �������

����� �������� �������� ��� �� ��������� �������� � ���� ���������. ���� ����� ����� �������� (������ 4 �������� d �� ���������) �������� ������� q1, q2, q3, q4 �������� ������������ ������� d � ������ ������� �� ������ �����. ����� ����������, ��� ������ ��������� q1, q2, q3 � q4 ������ ������ ������ �������� d � ��� ��� ������ �� ������. � �� ����, ��� ����� ���������� ������������� ����� ����� ���� � ������. ���� ������������, ��� �������� ������ q1 ��� ����������� ���� ���������� �������� d, �� ���������, ��� ����� ������� ���� ������ d ���������� ���� � ���� � �� ��� ��� ��� ��������. ���������, � �� ����� ������� ��� ����� ����� ����� ���������� � �������.

��� ���� ����� �� �������� ����.

��� �������, ��� ������������ ���������� ����� ������, ��� � ���� ���� assign qq = 1 << {r2,r1}; ������ � ���� ������� ������ ����� �� ����� ������������, ��� ��������� ������� ����������� �����. � ����� ������������ � ASIC �������� ������ �� ������������������, ���� ���������� ������� ������� ���� ������ � ����� ������� ������ ����� ����������, ������� �����������������. �� ���� ����������� ����� ��������, ��� ��� ������� � ��� ��� ���������.

� ���� ������ � ������ ��������� �������� ���������� ���� � ���, ��� ������� ����������� ������� ��� ������������� ����� ������� ������. ����� ���� ��� ���-�� �� ����� �������� � ��� ���������� �������������� ����������� ��������� ����� ����. � ������ � ����������������� ��� ����� ���� ����� ������������� ���� ����������� (�� ��� ���� � ����). ��� ����� ������ ���������� � ���� �� ���������� ������� ��������� �����.

� ���-�� ����� ������������ �� ���������� ����� �� Double-Edge-Trigger. ���� ����������� � ���, ����� ������������ ��� ������� ���������� ������ ��� ������ �������� �������. � �����, ��� ������������� DET �������� �������� � ���� ��� ��� �� �������� ���������� ����� ������� ������� � ��� ���� ������ � ������ ��� ������� �������� �����������������. � �������������� ���� ������ � ���� �������� ��� � ���� � �� �������. ����������� �� ���� ������� �����.

����� � ��������� ������� ����������� ����� ������������ � ������ ��� ���� � �������������� �������: ������ ����� � DET ���������� ��������� � ���� ������������ ������� ������, ��� ������.

����������� ������, ��� ����, ���������. ��, � ���������, ������� �������� ����������. �� ��������� ���������� ��� ������� ������ � ����������. � ����� ����������� ��������� ��������� ���� � ����, ���� � ��������� � ��� �� ������ � �� ������. ������ ModelSim ������ ����������� � ���������� ����������� ����.

��������� � ���������! �������� �������!

| �������������� | « ����. ������ — � �������� — ����. ������ » | ��������: [1] [�����] |